#### Fall 2012 JHU EE787 MMIC Design Student Projects Supported by TriQuint Semiconductor, Applied Wave Research, and Agilent Inc. Professors John Penn and Dr. Willie Thompson

Balanced Amplifier—Terron Ellerbe BroadBand Amplifier—Brandon Butterworth BroadBand Amplifier—Jason Hodkin BroadBand Amplifier—Shannon Marshall BroadBand Amplifier—Brian Billman BroadBand Amplifier—Robert Reyes Low Noise Amplifier—Michael Coon BroadBand Low Noise Amplifier—John Novak

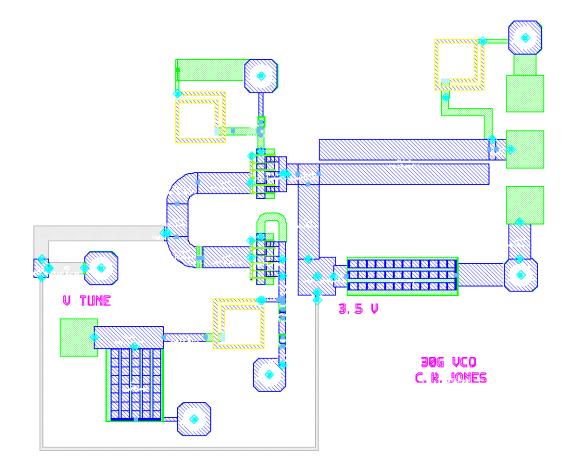

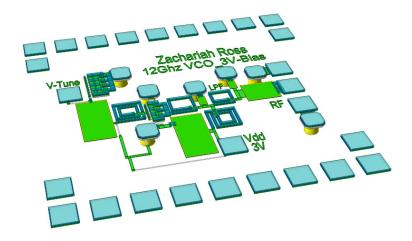

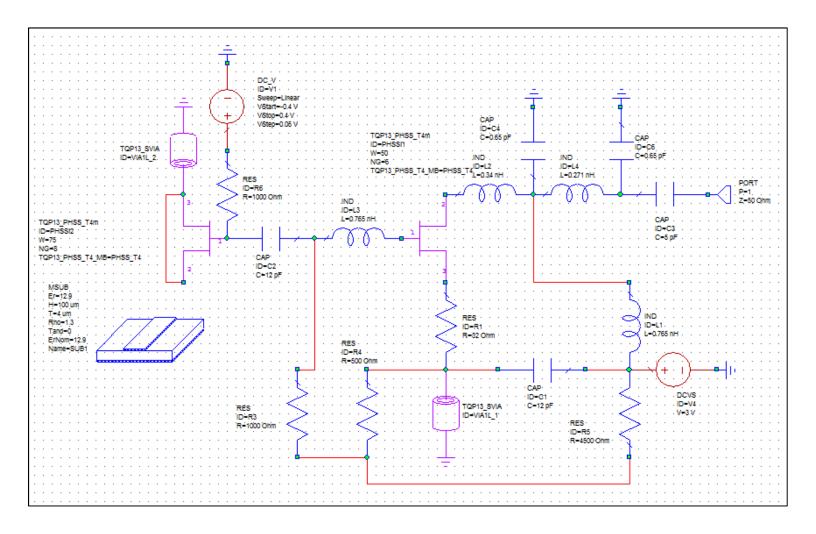

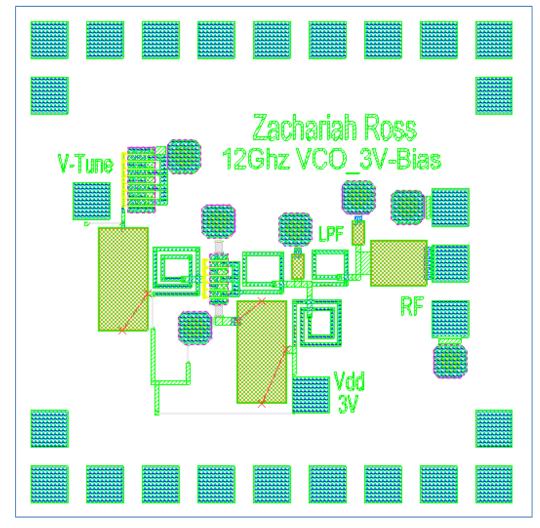

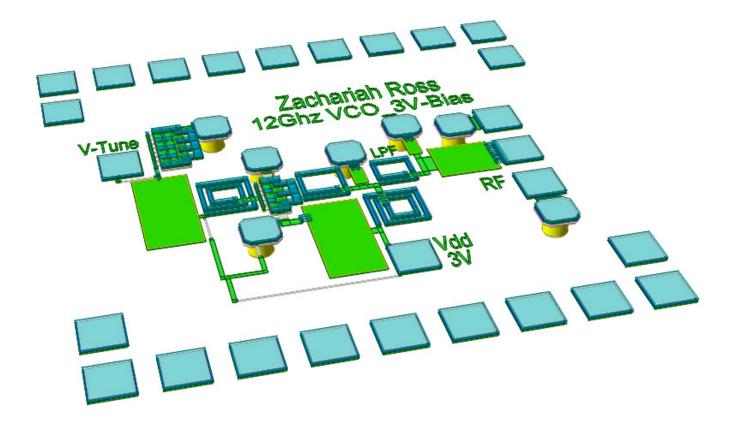

Voltage Controlled Oscillator—Zach Ross

### JHU12ALL Fall 2012 JHU MMIC Class TriQuint TQP13 Quarter tile 5x10mm

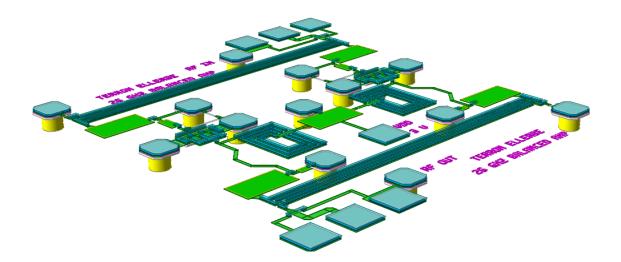

## **26 GHz Balanced Amplifier**

**Terron Ellerbe**

MMIC Design – EE 525.787

JHU Fall 2012

#### Abstract:

This report details the design of a K Band single stage balanced amplifier Monolithic Microwave Integrated Circuit (MMIC) utilizing 90 degree lange couplers. The 300 um amplifiers are designed to operate using a single 3V drain source. This circuit was designed using the TQP13 process and fits within the 60 mil x 60 mil Anachip layout.

#### 1. Introduction

Balanced amplifiers are devices that use ninety degree directional couplers with two identical amplifiers. This circuit takes advantage of the good input and output match and the wide bandwidth of the coupler to improve performance. Any mismatches that the amplifiers see at their input and output are canceled through the couplers in this balanced configuration, so it looks like the circuit is seeing 50 ohms. The balanced amp circuit yields approximately 3 dB more in output power compared to what a single amplifier will see.

#### 2. Design Approach

#### a. Design Goals vs. Performance

| Parameter          | Design Goal     | Expected Performance |  |

|--------------------|-----------------|----------------------|--|

| Input Return Loss  | > -20 dB        | ~ -21.8 dB           |  |

| Output Return Loss | > -20 dB        | ~ -22.3 dB           |  |

| Gain               | > 8 dB          | ~ 8.5 dB             |  |

| Noise Figure       | < 4 dB          | ~2.5 dB              |  |

| Peak Output Power  | > 8 dBm         | ~ 9.6 dBm            |  |

| Drain Voltage      | 3 V             | 3V                   |  |

| Layout             | 60 mil x 90 mil | 60 mil x 60 mil      |  |

#### Table 1 - Design Goals versus Expected Performance

#### b. Tradeoffs

- For this design I went for a simultaneous conjugate match on the amplifier in order to try to attain the best gain and power available. I designed the amp so that the gain peaked at my desired frequency, but this was at the expense of having a more bandwidth.

- By adding a second ground-via to the source in parallel with the first, I traded some stability on the small signal amplifier in order to achieve more gain by halving the inductance seen at the source.

#### c. Design Methodology

The original goal of this project was to fit a 26 GHz balanced amplifier in a 60 mil x 90 mil anachip layout. The frequency 26 GHz was chosen due to the fact that it was close to the limit of the equipment available to test the circuit and the higher frequency gave me the best chance to fit the two couplers into the layout. The design of this circuit was done in two stages. The first step was to design the small signal amplifier and coupler circuits individually for performance and lay them out individually. Once these sub-circuits were complete the second step was to combine these circuits in a manner that allows the circuit to fit into the layout while maintaining performance.

#### Small Signal Amp Design

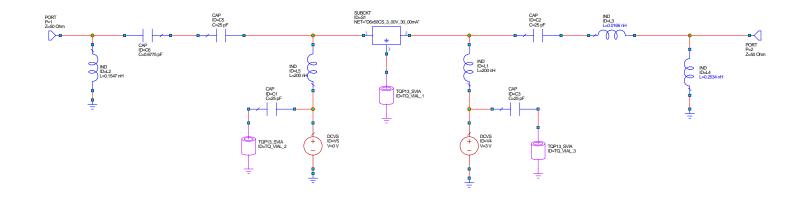

The first step in designing the small signal amplifier was to look at the stability of the pseudomorphic high electron mobility transistor (PHEMPT) and then add the matching circuitry. Looking at the stability of the PHEMT device showed that I did not need a stabilizing resistor above 21 GHz, however a large shunt resistor was added to the gate of the PHEMT in order to keep the gate from floating. The next step was to design the input and output matching networks for the amplifier using ideal elements. The input was matched for the best available gain and the output was matched for the best available gain and the output was matched for the best available power. The input matching network consisted of a shunt 0.09 nH inductor and a series 1.41 pF capacitor. The output matching network consisted of series inductance of 0.355 nH and a shunt 0.19 pF capacitor.

The next step in designing the small signal amplifier was to replace the ideal matching elements with lossy elements and add the bias circuitry. The first step in converting the circuit from ideal elements to one using the TQP13 process was replacing the S parameter data for the PHEMT with TOM4 model. The ideal capacitors were replaced with TQP13 capacitors, the ideal inductors were replaced with TQP13 spirals and the ideal grounds were replaced with TQP13 vias. The TQP13 elements take into account resistive and reactive effects that the ideal elements do not, and due to these effects the passive elements needed to be tuned slightly to get the performance back to the same operating frequency. I chose to have the 300 um PHEMT biased at 3V and approximately 30 mA. When adding the DC circuitry to the amplifier I added a large inductor to act as a RF block and a large bypass capacitor. For this design only a drain voltage was added to get close to this bias point but in future iterations circuitry to add a gate supply will probably be added as well.

The final step in this design was to add interconnects and begin working on the circuit layout. By having the design of the amplifier at 26 GHz, the interconnects needed for the circuit significantly shifted the operating range down in frequency. At

this frequency the interconnects needed to be as small as possible, however this was causing the design to be too compact and coupling between the lines became a concern. In order to avoid this issue I removed the inductor elements from the design and replaced them with microstrip lines of equivalent inductance and retuned the capacitors slightly to get the operating frequency back where I wanted it. This allowed me to keep my input and output match while spreading out the layout enough to avoid lines being too close and coupling with each other.

#### Coupler Design

For the coupler design I decided to go with the lange coupler instead of the branchline coupler because it would consume less space in the layout. The mlange component in Microwave Office was used to simulate the electrical performance of the lange coupler. The TXLine tool was used to determine a quarter-wave line at 26 GHz. This value used as a baseline for the coupler and then tuned to get the element back to the desired operational frequency range. A line width if 7 um and space of 8 um was chosen to get as close to 3 dB coupling as possible from the device.

#### Balanced Amplifier Design

With all of the individual circuits completed I placed the individual amplifier and lange coupler circuits in the same schematic. When adding the interconnects in between the sub-circuits and to the RF pads at the edge of the board I had to make sure that I kept the loss of these lines to a minimum so that my performance is not affected too much. In order to accomplish this I either kept lines as short as possible for the normal 10 um line width or made the lines wider for longer line runs. With the subcircuits connected, the last item to add to the circuit was the ground via for the RF pads.

#### 3. Simulations

- a. <u>Linear</u>

- i. Small Signal Amplifier

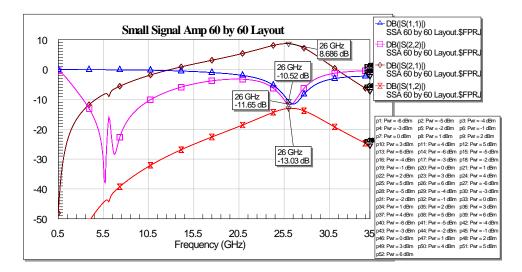

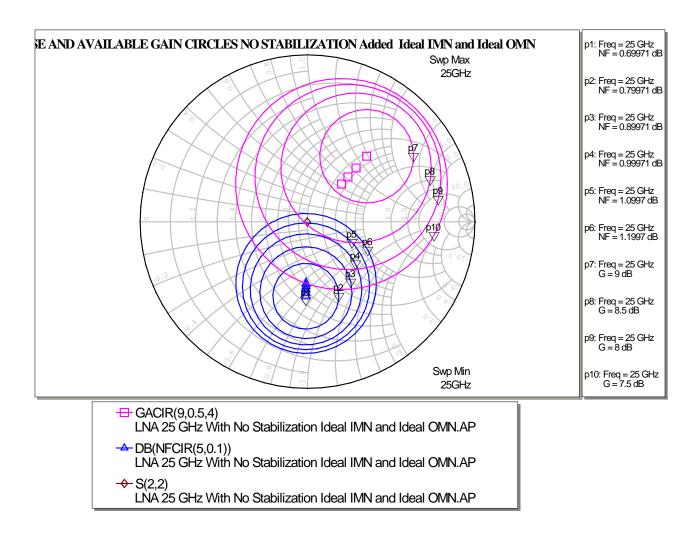

Figure 1 - Small Signal Amplifier S-Parameter Simulation Results

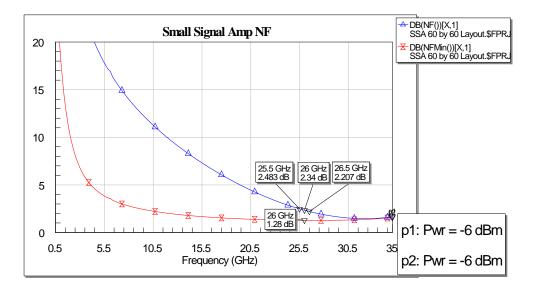

Figure 2 - Small Signal Amplifier Noise Figure Simulation Results

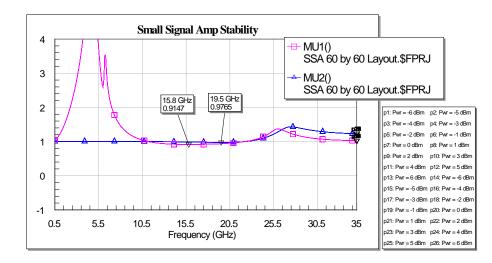

Figure 3 - Small Signal Amplifier Stability Simulation Results

The simulated results for the small signal amplifier show that the amplifier has 8.686 dB of gain at the desired frequency of 26 GHz, but the device is pretty narrow band. The input and output return loss is decent at -10.52 dB and -11.65 dB at 26 GHz and the noise figure less than 2.5 dB over the desired band. By adding the second via to the source of the PHEMPT I was able to achieve more gain for the circuit however, the stability of amplifier went from unconditionally stable up to 35 GHz conditionally stable from 10.5 GHz to 20.5 GHz and unconditionally everywhere else. I did not think this region of conditional stability would cause a problem because the return loss in that region did not go positive in that region. I also felt that the loss of the langes and the interconnects in the final circuit would help with stability.

#### ii. Lange Coupler

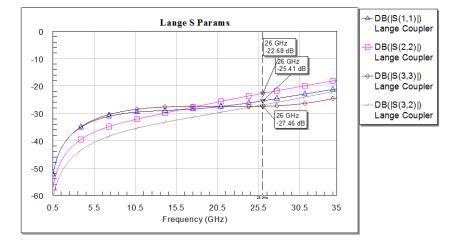

Figure 4 - Lange Coupler S-Parameter Simulation Results

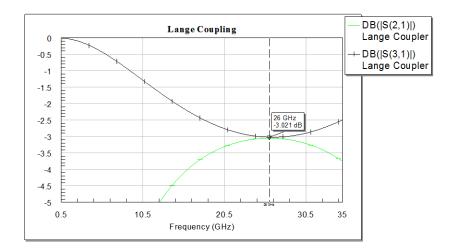

Figure 5 - Lange Coupler Insertion Loss and Coupling Simulation Results

The lange coupler has broader band performance and input and output return loss values that are better than -20 dB. The simulation also shows that coupling is very close to 3 dB which means that the power delivered to the two amplifiers will be divided evenly.

#### iii. Balanced Amplifier

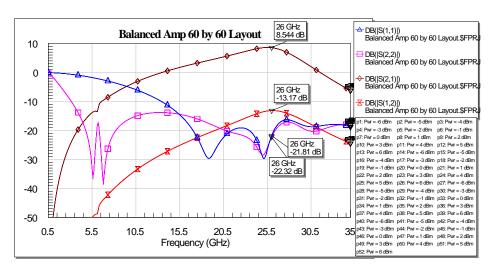

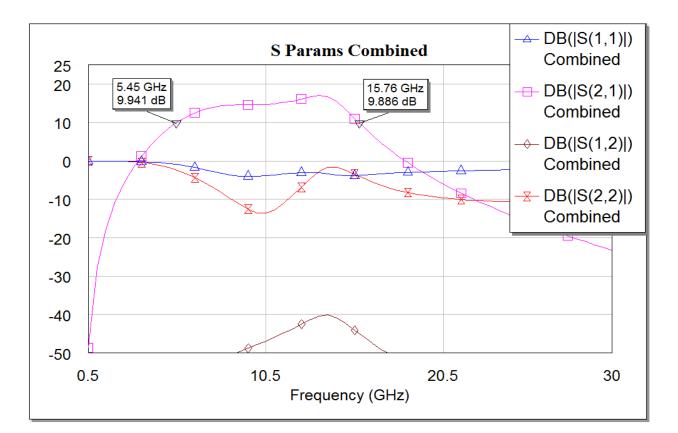

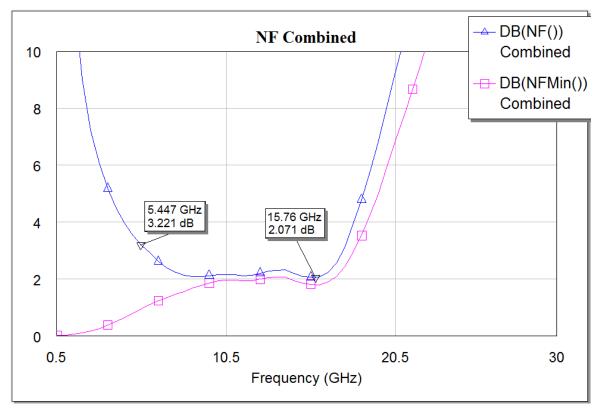

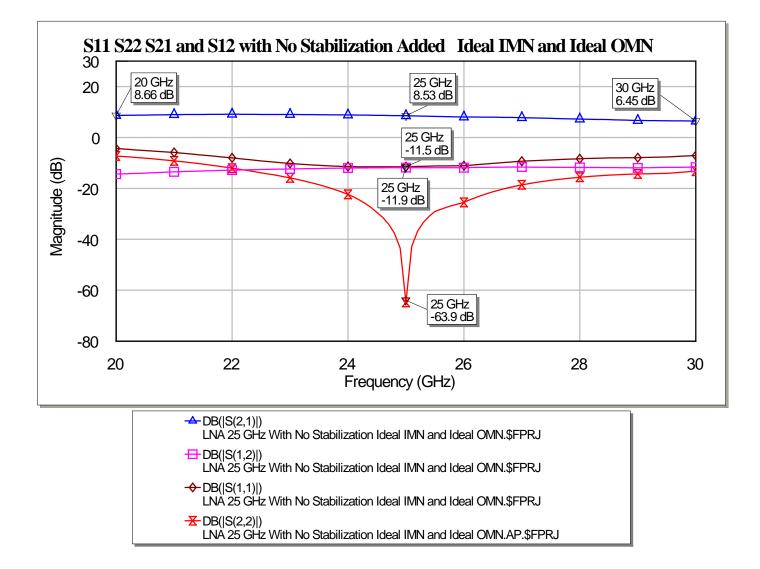

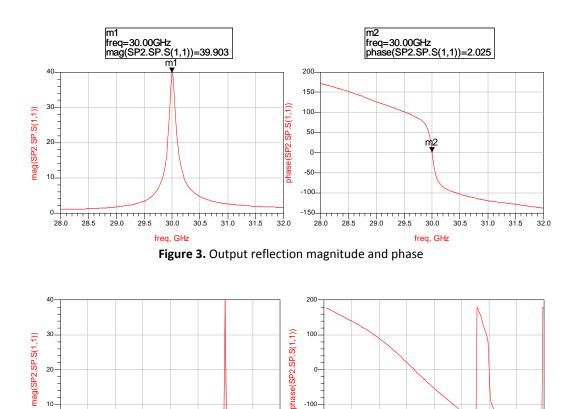

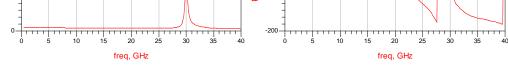

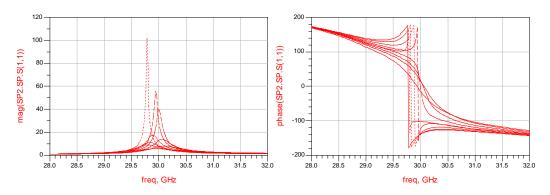

Figure 6 - Balanced Amplifier S-Parameters Simulation Results

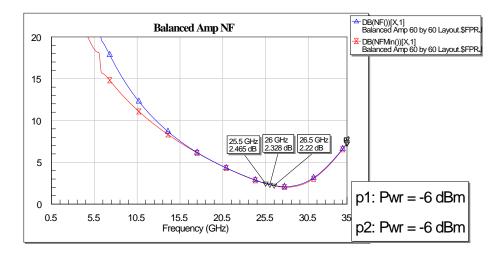

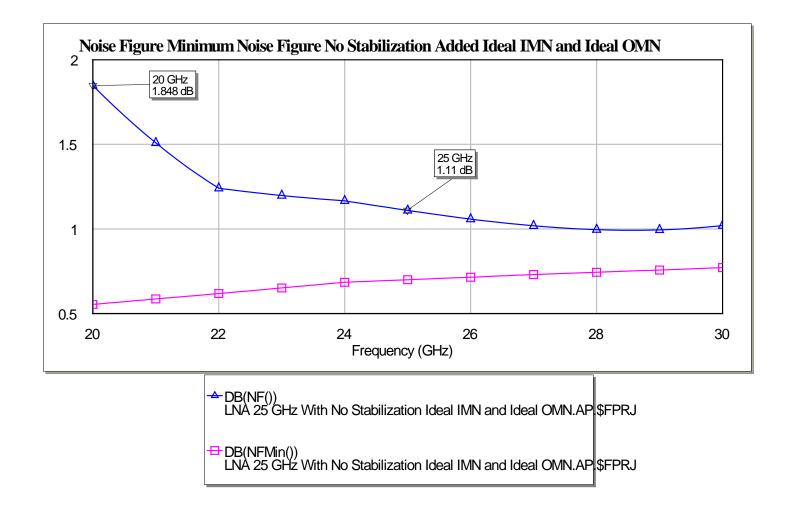

Figure 7 - Balanced Amplifier Noise Figure Simulation Results

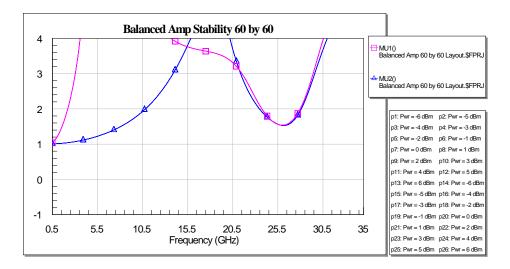

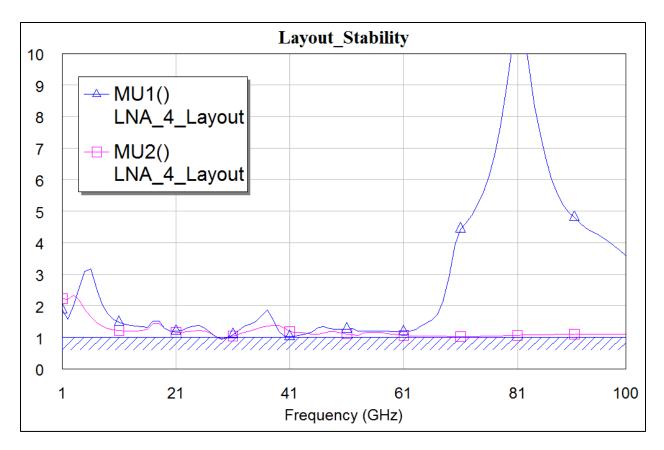

Figure 8 - Balanced Amplifier Stability Simulation Results

The simulated results for the balanced amplifier show that the amplifier has 8.544 dB of gain at the desired frequency of 26 GHz. The input and output return loss improved to -21.81 dB and -22.32 dB at 26 GHz due to the return loss of the lange coupler. The balanced amplifier still has a noise figure less than 2.5 dB over the desired band, but is unconditionally stable up to 35 GHz.

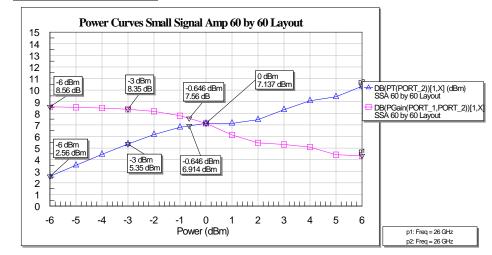

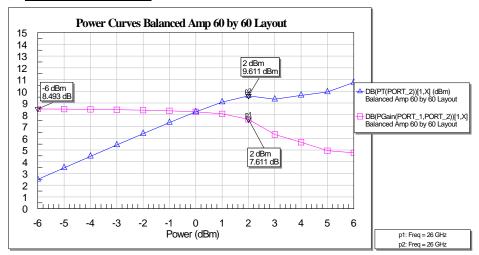

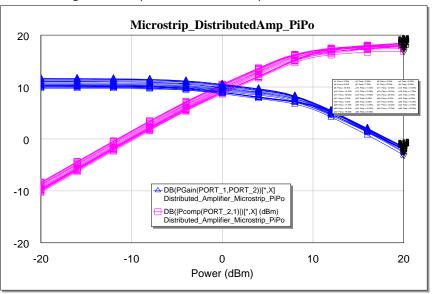

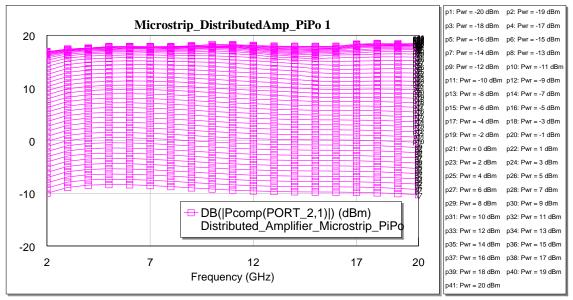

b. Non-Linear

When looking at the non linear performance of the individual small signal amplifier and the balanced amplifier the power of the device in both cases began to saturate and then continues to go linear. I don't believe that this behavior is real, but instead is an artifact of simulation having issues converging at these higher power levels. Assuming that the point where the power first starts the saturate is indeed correct, the peak output power for the small signal amplifier is 7.137 dBm and the peak output power for the balanced amplifier is 9.611 dBm.

#### i. Small Signal Amplifier

Figure 9 - Small Signal Amplifier Power Simulation Results

#### ii. Balanced Amplifier

Figure 10 - Balanced Amplifier Power Simulation Results

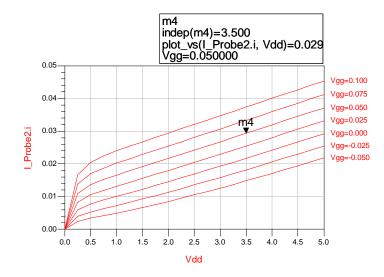

#### c. <u>DC</u>

Figure 11 - Balanced Amplifier Bias Simulation

With only applying 3 volts applied to the Drain DC pad, the simulation is showing the device is operating at 2.97V and 26.9 mA. The addition of a small gate voltage would help get the circuit to the desired 3V, 30 mA operating point that was desired.

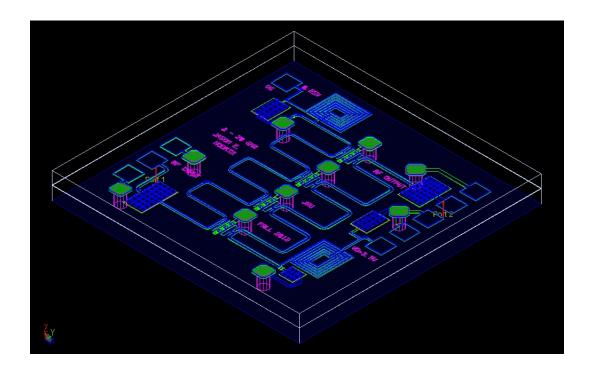

#### 4. Schematic and Layout

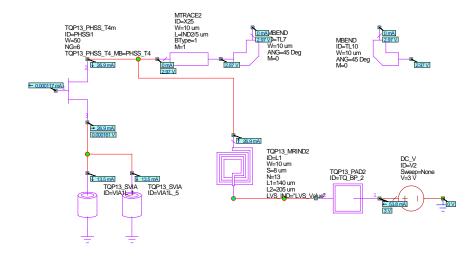

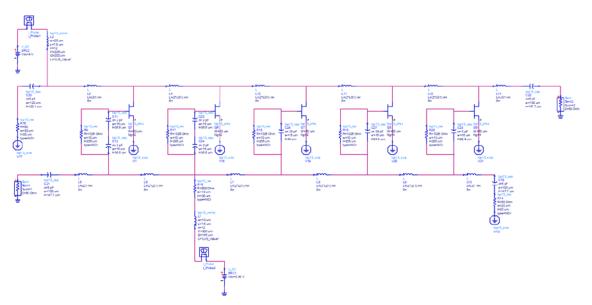

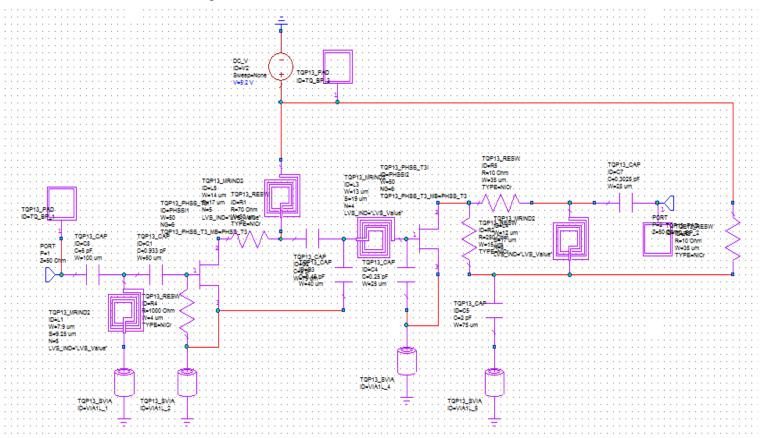

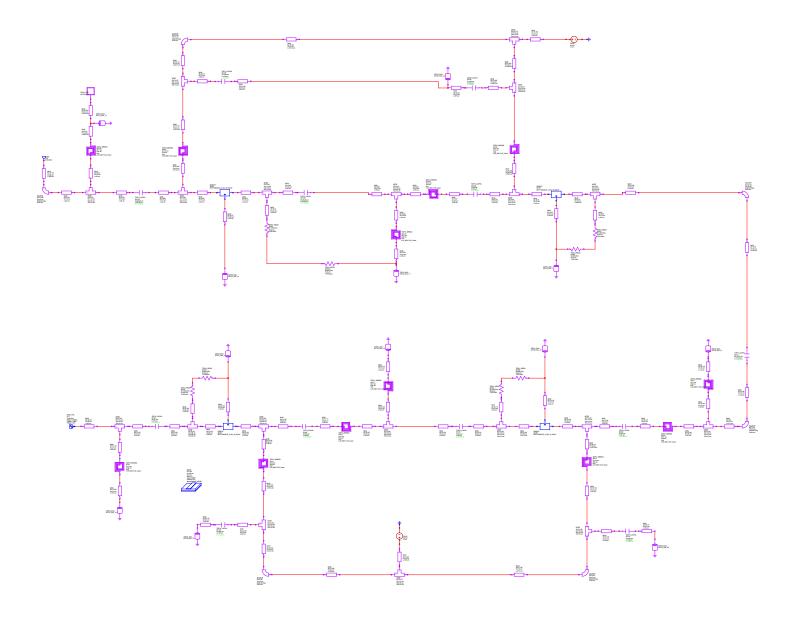

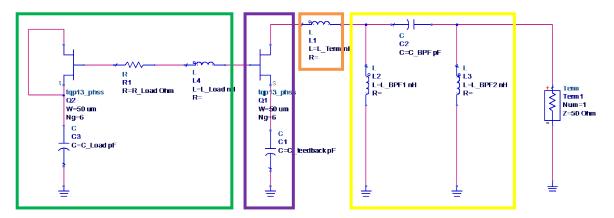

Figure 12 - Balanced Amp Layout Schematic without interconnects

Figure 13 - Balanced Amp Layout

#### 5. <u>Test Plan</u>

S-Parameter and Power Measurement:

- 1. Using a power supply and a needle probe apply 3V to the drain of the balanced amp.

- 2. Add Ground-Signal-Ground (GSG) probes to the network analyzer input and output cables.

- 3. Characterize cable loss so that it can be taken removed from the measurement results.

- 4. Apply GSG probes to the RF input and the RF output of the chip

- 5. Calibrate the Network Analyzer to sweep frequency from 25.5 GHz to 26.5 GHz in 0.1 GHz steps with the input power level set to -6 dBm and take S-Parameter data.

- 6. Set the network analyzer to 26 GHz and the input power level of -6 dBm and measure the output power.

- 7. Slowly increase the input power in 1 dB steps and measure the output power at each point until the device compresses.

Noise Figure Measurement:

- 1. Using a power supply and a needle probe apply 3V to the drain of the balanced amp.

- 2. Connect a noise source to the input of the circuit and connect the output of the circuit to a noise figure analyzer.

- 3. Configure the noise figure analyzer to take noise figure measurements from 25.5 GHz to 26.5 GHz.

#### 6. <u>Summary and Conclusions</u>

The design met the performance goals that I set for the balanced amp and was able to fit into a smaller layout foot print than I was originally expecting. The next step for this iteration of the design would be running an electromagnetic simulation on the circuit to make sure the circuit will behave as expected. For a second iteration of this design I would look into using the space in the layout more efficiently. This would allow me to broaden the bandwidth of the device by using more elements in the matching networks and add DC circuitry to the gate of the PHEMTs for the addition of a potential gate supply.

# 2-20GHz LNA Project 525.787 MMIC Design

**Brandon Butterworth**

Fall 2012

#### Abstract

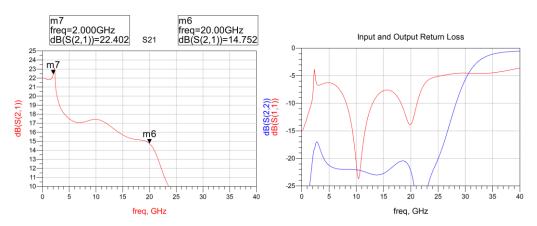

The design in this report is a cascode distributed amplifier. The goal of the design was to create an amplifier with a noise figure of <3dB, while still maintaining an output compression point of 17dBm over the range of 2-20GHz. The process used is Triquint's TQP13, and the simulations were performed in Agilent's ADS 2011.10. The final amplifier has >13dB of gain over process variations, an excellent match on the output, and a typical noise figure of 2.0dB.

#### Introduction

This report outlines the design approach taken for a distributed cascode amplifier, as well as the final results. Included are Monte Carlo simulations, as well as the expected test plan as soon as the die is fabricated. Overall, the simulations appear to be promising for a decent amplifier. Nominally the gain is greater than 14.5dB over the range of 2-20GHz, with a return loss of <-15dB. Furthermore, the noise figure is less than 3dB over the frequency of interest.

#### **Design Approach**

The design approach for this amplifier was to initially get a rough idea on what is achievable in this process, and whether the specification and goals seem realistic. So a rough sketch of a distributed amplifier, without any interconnect, was performed. This initial design, which unfortunately was not saved, proved that the design goals seem to be achievable, all except for the gain that I wanted out of the amplifier. The initial distributed amplifier only had 4 stages, and had about 10dB of gain at 20GHz. This was using a 50um, 6 fingered device.

After this point, there was an investigation into a cascade topology. This approach seemed very promising, until I could not get an oscillation quelled at 28GHz once interconnects were added. Cleaning up the layout proved to remove the high frequency oscillations. Ultimately, I adjusted the size of the transistor from 50um, 6 fingers down to 40um, 6 fingers to improve the output return loss.

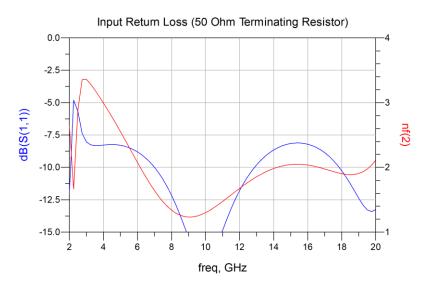

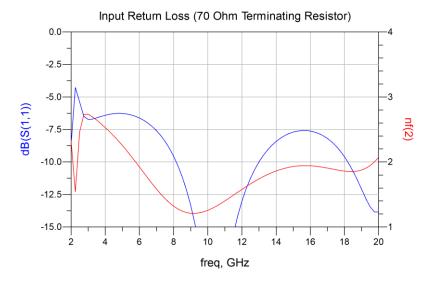

The final cascode distributed amplifier has a few slight adjustments to the cookbook distributed amplifier topology. The first noticeable change is the termination resistor on the input transmission line. The noise from the 50 ohm termination resistor was dominating the noise figure at low frequencies. This termination resistor as a result was increased in order to decrease the contributions from this noise source. An alternative method that was investigated was to use an active termination, but in order to simplify the biasing, the larger resistor was instead used. As you can see below, at low frequencies the degradation of the noise figure when decreasing the gate line terminating resistor from 70 ohms to 50 ohms is on the order of 0.6dB. The degradation in input return loss was about 2dB. The trade-off therefore was made to degrade the input return loss in order to improve the low frequency noise figure.

Figure 1 Input Return Loss and Noise Figure (50 Ohm Input Term)

Figure 2 Input Return Loss and Noise Figure (70 Ohm Input Term)

Another problem that came up during the design process was the lack of space on the Anachip. As a result, I am missing two inductors on the gate transmission line that could have optimized the gain and return loss of the amplifier.

| Parameter           | Specification          | Goal                   |

|---------------------|------------------------|------------------------|

| Operating Frequency | 2 to 20GHz             | 1 to 22GHz             |

| Gain, S21           | > 12dB                 | >15dB                  |

| NF                  | <3.0dB                 | <2.5dB                 |

| S11                 | <-5dB                  | <-10dB                 |

| S22                 | <-10dB                 | <-15dB                 |

| Output P1dB         | >+17dBm                | >+17dBm                |

| Stability           | Unconditionally Stable | Unconditionally Stable |

| Power Consumption   | None                   | <500mW                 |

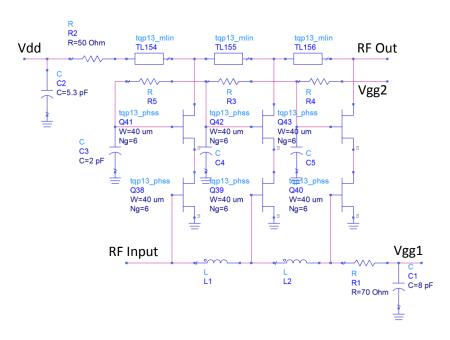

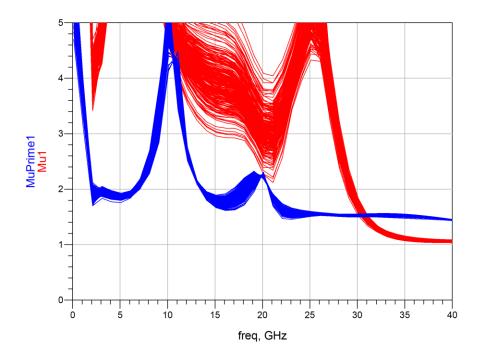

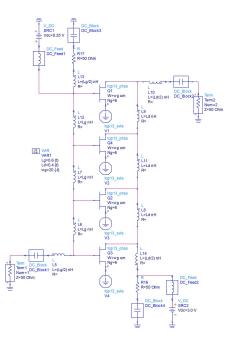

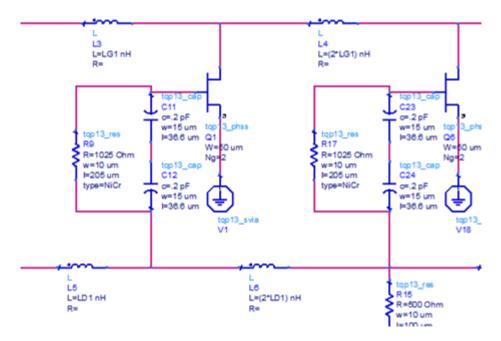

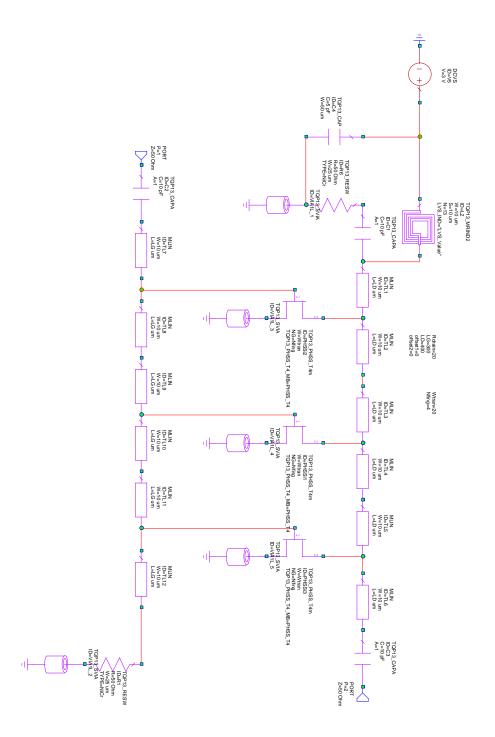

#### Schematic

A simplified schematic is shown below for the cascode distributed amplifier. Not shown below are the drain stabilization resistors. One note about the schematic is the topic of biasing. Both Vdd and Vgg1 require low frequency terminations in order for this amplifier to work well below 2GHz. The simulations in this report are assuming a low frequency termination, with values of 1000pF and 100pF. The simulations do incorporate 0.4nH of bondwire inductance, as well as an inductance in the capacitors on the order of 0.45nH. None the less if one was to bias the amplifier through the Vdd port, the required voltage is 9V due to the drop across the 50 ohm termination. If a designer does not want to consume 9V @ 65mA, an external bias tee can be used on the RF out port. This will cause the amplifier to operate at 6V 65mA. This reduces the power used of this amplifier from 620mW to 390mW.

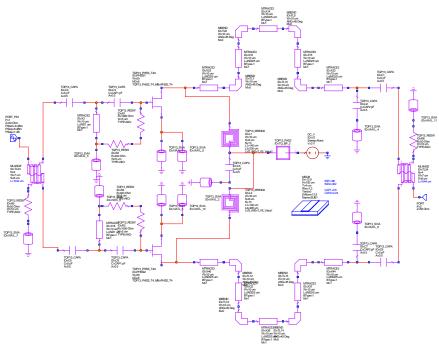

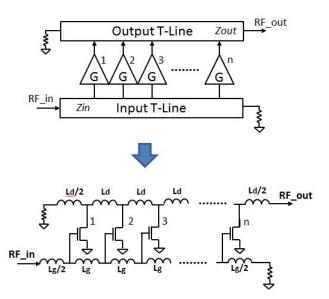

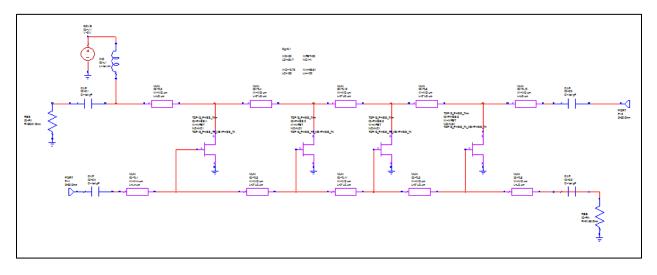

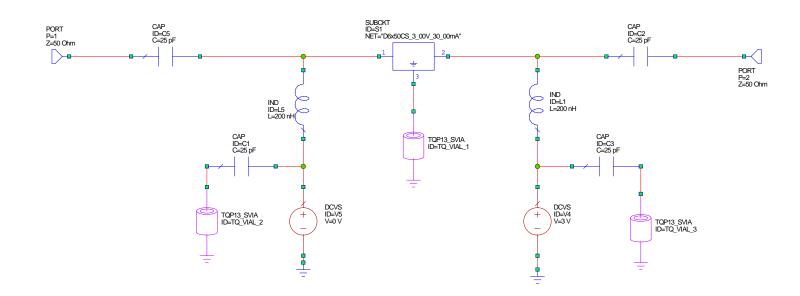

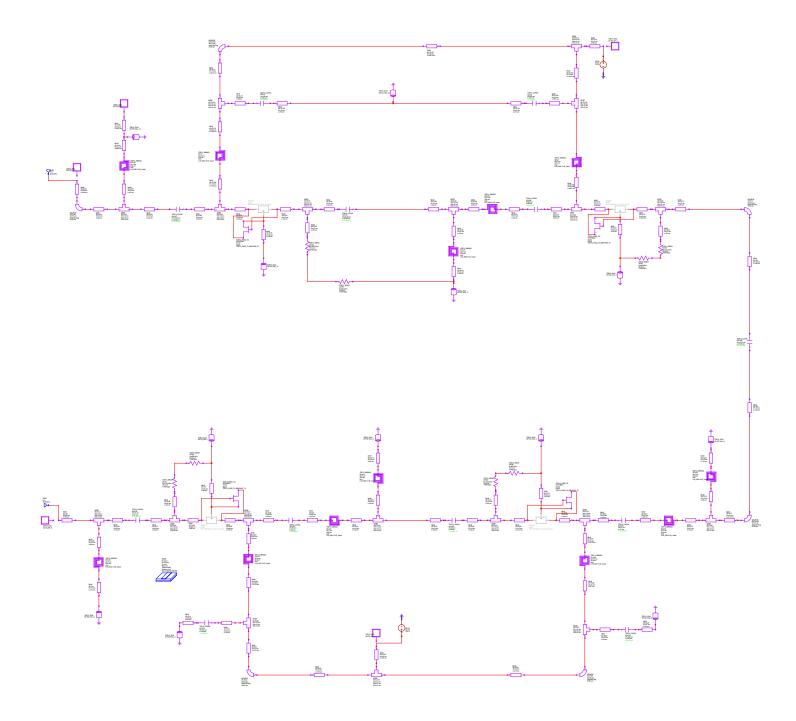

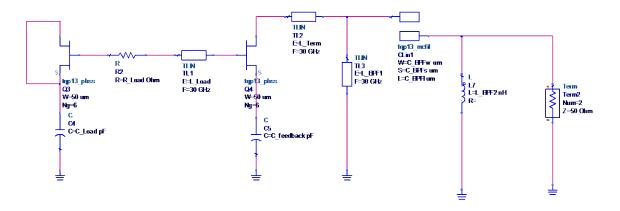

**Figure 3 Simplified Schematic**

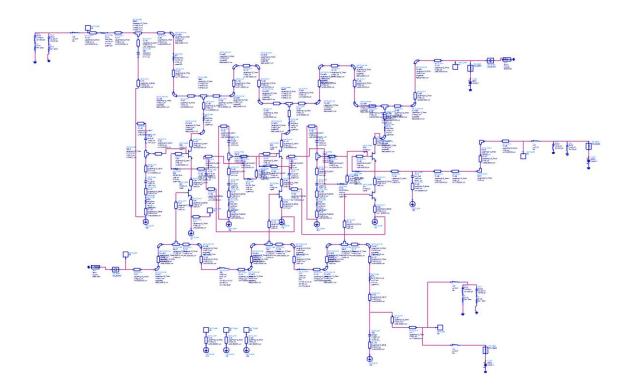

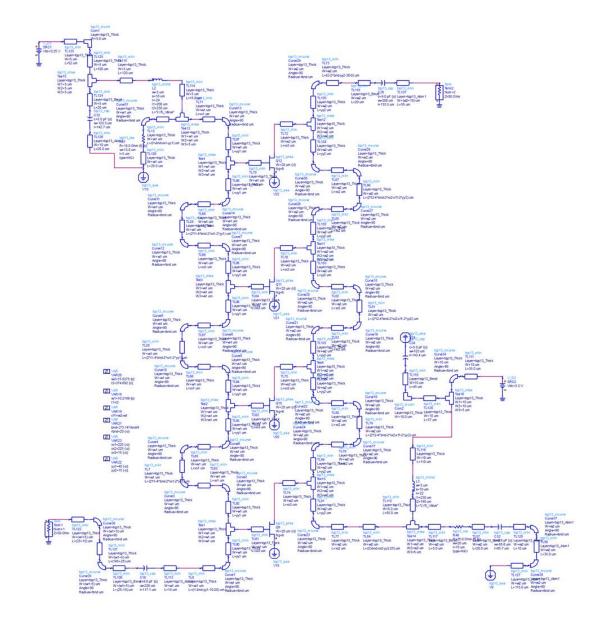

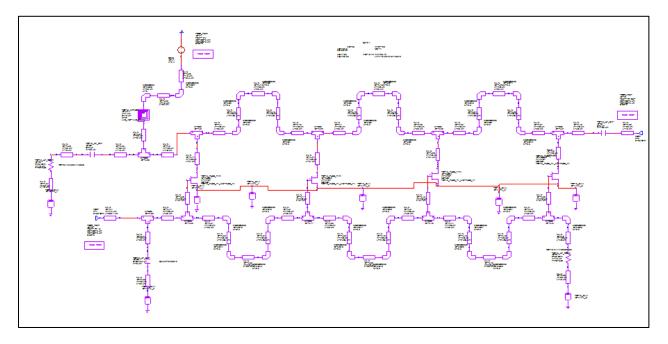

The full-schematic is below, including all of the interconnects.

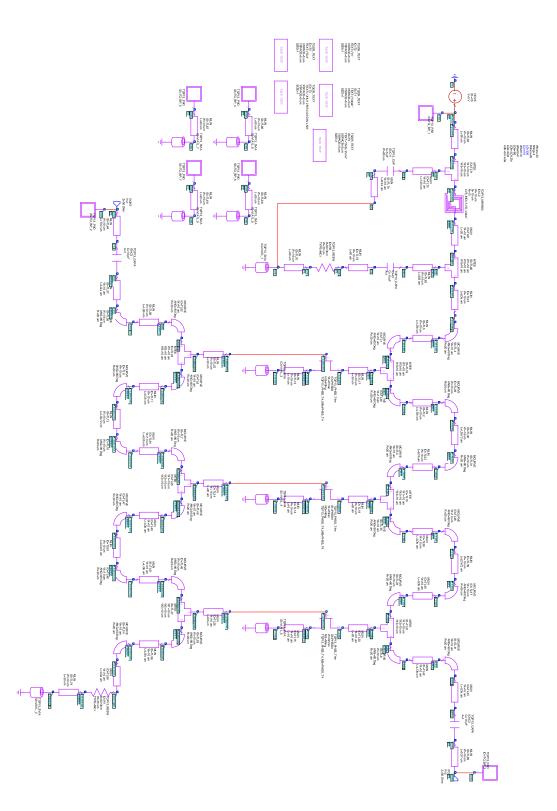

**Figure 4 Uncensored Schematic**

#### **Simulations**

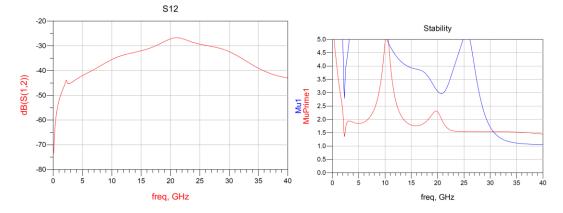

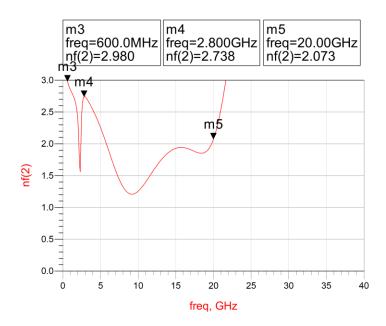

The S-Parameters, and noise figure is below. These results are using the TOM4 Triquint Nonlinear model. The gain of the distributed amplifier is not necessarily flat, but it was not one of the design elements that I placed much emphasis on.

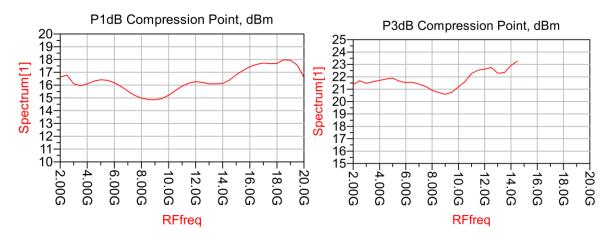

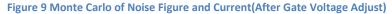

**Figure 8 Compression Points**

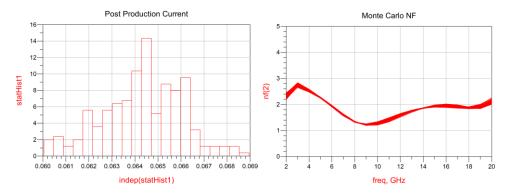

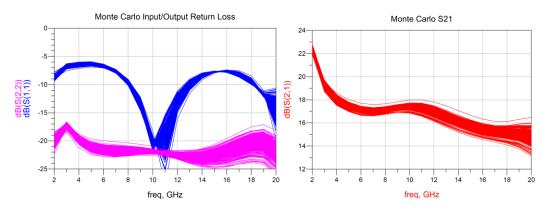

As a final part of this project, I also decided to perform a Monte Carlo analysis using historically measured values. This Monte Carlo analysis was performed after the submission of the layout. I performed a post-production optimization to the gate voltage of the bottom-FET, and simply added 3V to Vgg1 in order to get Vgg2. The Monte Carlo results are below, and it shows some wide variability due to process sensitivities, and the lack of feedback. The units for the post production current plot below are in Amps.

Figure 11 Monte Carlo of Stability

Layout

#### Test Plan

**Expected Equipment Requirements:**

- 3 DC Probes (Vgg1, Vgg2, Vdd)

- Three RF Probes

- Noise Diode/Analyzer

- Signal Generator

- Network Analyzer

- Spectrum Analyzer

There will be three measurements to be performed. The measurements are to characterize the S-Parameters, the noise, and finally the compression of the amplifier. These various measurements are outlined below, but they all follow the following biasing procedure. These instructions assumes the tester understands that cables are required between the test equipment, and by no means are these instructions intended for a person that doesn't know what RF stands for.

#### **Biasing Procedure**

Set Vgg1 to 0V, and Vgg2 toVgg1+3V. If you are biasing from the Vdd line, slowly increase the voltage to 9.25V. Adjust Vgg1 until you get to a quiescent current of 65mA. Maintain the Vgg2=Vgg1+3.0V relationship.

#### <u>S-Parameter Measurement</u>

Connect the amplifier to the network analyzer using the probe-station. Make sure the input power into the amplifier is <-10dBm in order to accurately measure the small-signal parameters. Furthermore, ensure the network analyzer is properly calibrated. The exact calibration is to be determined.

#### Noise Figure Measurement

Calibrate the noise figure (ie perform a 2<sup>nd</sup> stage correction). This removes the noise contribution of the spectrum analyzer or the noise figure meter. From there, connect and bias the amplifier, and measure the noise figure of the device.

#### Compression Measurement

Determine the losses/inaccuracies out of the signal generator and into the spectrum analyzer over the frequency range of 2-20GHz. Record these values. Sweep in the input power into the amplifier until the gain of the amplifier drops by 3dB. Record the 1dB and 3dB compression points. Perform this measurement between 2-20GHz.

#### **Summary and Conclusions**

The table at the end of this section summarizes the design, with that of the specifications and goal. All except for the output power are taken over the process variation.

The gain meets the specification, but does not completely hit the goal of 15dB at 20GHz over process variations. This is a little disappointing, but overall the design appears to be relatively solid. Typically that amplifier has a 2.0dB noise figure, output return loss at the worst case is -16.5dB. The output power does miss its specification and goal. This was observed after the submission of the layout. In retrospect, larger transistors may help optimize the output power for the distributed amplifier.

| Parameter           | Specification          | Goal                   | Design            |

|---------------------|------------------------|------------------------|-------------------|

| Operating Frequency | 2 to 20GHz             | 1 to 22GHz             |                   |

| Gain, S21           | > 12dB                 | >15dB                  | 13dB @ 20GHz      |

|                     |                        |                        | Over Process      |

|                     |                        |                        | Variations        |

| NF                  | <3.0dB                 | <2.5dB                 | <2.9dB Worst Case |

|                     |                        |                        | <2.0dB typical    |

| S11                 | <-5dB                  | <-10dB                 | <-5.7dB           |

| S22                 | <-10dB                 | <-15dB                 | <-16.5dB          |

| Output P1dB         | >+17dBm                | >+17dBm                | >14.8dBm worst    |

|                     |                        |                        | case              |

|                     |                        |                        | >16dBm typical    |

| Stability           | Unconditionally Stable | Unconditionally Stable | Unconditionally   |

|                     |                        |                        | Stable            |

| Power Consumption   | None                   | <500mW                 | 390mW with        |

|                     |                        |                        | external bias tee |

|                     |                        |                        | 600mW without     |

|                     |                        |                        | external bias tee |

## $2\mathchar`-20$ GHz Distributed Amplifier MMIC Design

Jason E. Hodkin

December 8, 2012

## Contents

| 1        | Abstract                 | 4  |

|----------|--------------------------|----|

| <b>2</b> | Introduction             | 4  |

| 3        | Design Approach          | 6  |

|          | 3.1 Design Goals         | 6  |

|          | 3.2 Device Size and Bias | 6  |

| <b>4</b> | Simulations              | 8  |

|          | 4.1 Ideal Simulation     | 8  |

|          | 4.2 Detailed Simulation  | 11 |

|          | 4.2.1 Linear             | 11 |

|          | 4.2.2 Nonlinear          | 12 |

| 5        | Schematic                | 15 |

| 6        | Layout                   | 16 |

| 7        | Test Plan                | 17 |

|          | 7.1 Linear               | 17 |

|          | 7.2 Nonlinear            | 17 |

| 8        | Summary & Conclusions    | 18 |

| Re       | eferences                | 18 |

## List of Figures

| 1  | Distributed amplifier block diagram and FET implementation    | 4  |

|----|---------------------------------------------------------------|----|

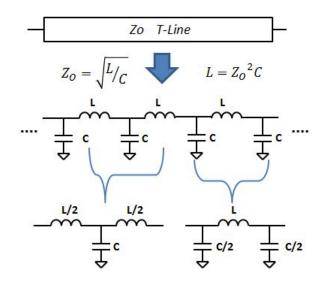

| 2  | Transmission Line implementation options with lumped elements |    |

|    | for distributed amplifiers                                    | 5  |

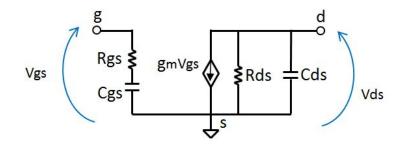

| 3  | Linear FET model                                              | 5  |

| 4  | Class-A bias and load-line                                    | 7  |

| 5  | Transconductance, gm, and polynomial curve fit.               | 8  |

| 6  | Cgs and Cds vs. frequency of 120um device                     | 9  |

| 7  | Ideal Distributed Amplifier Schematic                         | 10 |

| 8  | Ideal Distributed Amplifier Simulation Results                | 10 |

| 9  | Distributed Amplifier Performance, to 20GHz                   | 11 |

| 10 | Distributed Amplifier Performance, wide-band                  | 12 |

| 11 | Gain compression and OP1dB                                    | 13 |

| 12 | Third-Order Intercept                                         | 14 |

| 13 | Final 2-20GHz Distributed Amplifier MMIC Schematic            | 15 |

| 14 | Final 2-20GHz Distributed Amplifier MMIC Layout (ADS Layout)  | 16 |

## List of Tables

| 1 | Distributed Amplifier MMIC Design Goals                             | 6  |

|---|---------------------------------------------------------------------|----|

| 2 | Gain estimates for $n=4$ of 120 $um$ devices for both the extracted |    |

|   | 1st order transconductance and the process data-sheet specified     |    |

|   | transconductance.                                                   | 8  |

| 3 | Gate and drain transmission line inductance lumped element values   | 9  |

| 4 | Performance Summary                                                 | 18 |

#### 1 Abstract

The distributed amplifier architecture, shown in figure 1, is adopted for a wideband amplifier design utilizing an advanced low-cost GaAs PHEMT process for high frequency applications. The mmic design utilizes distributed elements for inductive sections, and achieves a moderate gain and output power with reasonable input and output return loss, while only utilizing four devices.

Figure 1: Distributed amplifier block diagram and FET implementation

#### 2 Introduction

The distributed amplifier has been utilized to achieve amplification since the early 20th century[1]. The distributed amplifier as a wide-band amplifier was most notably described by a co-founder of Hewlett-Packard Company[2]. An excellent overview of distributed amplifier mmic design can be found in [3]. The basic underlying concept of the design of a distributed amplifier is the utilization of transistor device capacitances in the synthesis of input and output transmission lines, which effectively acts to absorb device reactive parasitics, enabling wide-band operation. The synthesis of this artificial transmission line involves utilizing the gate capacitance (Cgs) or drain capacitance (Cds) of the FET device in lumped element form of a transmission line, figure 2. This lumped element perspective, however, does not eliminate the use of distributed elements in achieving the required inductance, as will be shown in later sections of this document.

Figure 2: Transmission Line implementation options with lumped elements for distributed amplifiers

The fundamental principle in achieving wide-band operation with this architecture is found by considering the Bode-Fano relation in equation 1 and the linear circuit model of a FET device, figure 3.

$$\int_{0}^{\infty} \ln \left| \frac{1}{\Gamma(\omega)} \right| d\omega \le \frac{\pi}{R_{ds} C_{ds}} \tag{1}$$

Figure 3: Linear FET model

In terms of the output transmission line for a distributed amplifier, evaluating the integral as described in [4], gives the bandwidth (BW), as a function of the drain impedance of the device as shown in equation 2. For an assumed constant return loss (RL), as  $C_{ds} \rightarrow 0$  then  $BW \rightarrow \infty$ . Ideally, achieving  $C_{ds} = 0$

(or  $C_{gs} = 0$  in the case of the input gate line) is accomplished by absorbing the capacitance into the matching network.

$$BW \le \frac{1}{2R_{ds}C_{ds}\ln|1/\Gamma|} = \frac{4.343}{R_{ds}C_{ds}RL(dB)}$$

(2)

Since the goal of the distributed amplifier design is to synthesize an input gate transmission line and output drain transmission line utilizing capacitive parasitics, the lumped element equivalent circuit of a transmission line provides the means to absorb device capacitances. This design approach is detailed in following sections.

#### 3 Design Approach

#### 3.1 Design Goals

The distributed amplifier was designed to meet or exceed the design goals of table 1.

| Band                   | 2 - 20    | [GHz]    |

|------------------------|-----------|----------|

| Gain                   | > 8       | [dB]     |

| Gain Flatness          | $\pm 1.5$ | [dB]     |

| Return Loss, in or out | > 8       | [dB]     |

| OTOI                   | >30       | [dBm]    |

| OP1dB                  | >17       | [dB]     |

| Chip Size              | 1.5 x 1.5 | $[mm^2]$ |

Table 1: Distributed Amplifier MMIC Design Goals

#### 3.2 Device Size and Bias

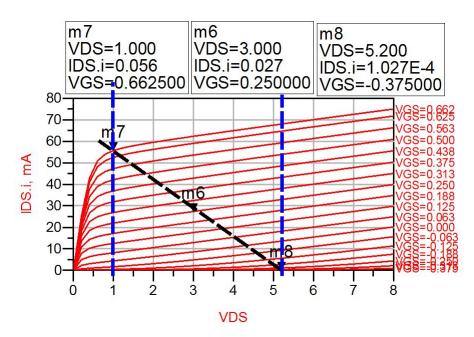

A Class-A bias was utilized and sizing of the device started by assuming a Bragg cutoff frequency (fco) of 20.5GHz, equation 3, and a linear device simulation showed that the largest device possible was 6x23um. However, in order to ensure wide-band operation while also maintaining device size amenable to a low number of stages, a 6x20um (or 120um) device was chosen for this design. This device size provides significant margin on cutoff, resulting in fco=25.36 GHz. It should be noted that a fundamental trade-off with this amplifier architecture resides in the device sizing for wide-band operation and the device periphery typically desired for high power or high linearity operation. It was found that for these devices the high frequency operation was limited by Cgs, that is, Cgs>Cds. The details of the Class-A bias can be seen in figure 4, where Vgs=0.25V with Vds=3.0V at Ids=27mA, with a resulting a load-line resistance of approximately 75.6 Ohms.

$$fco = \frac{1}{\pi \cdot Zo \cdot Cgs} \tag{3}$$

Figure 4: Class-A bias and load-line

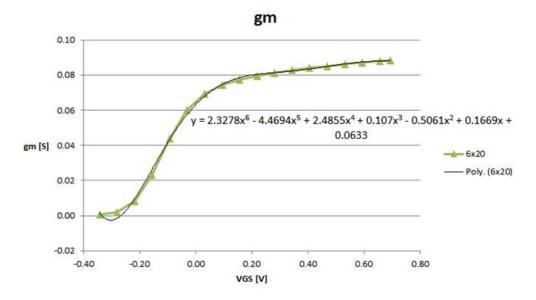

Given a device size and bias it is possible to estimate the number of devices required to meet the gain design goal. First an estimate of the device transconductance, gm, is necessary. The gm was extracted from the device dc IV simulation. It should be noted however that this is not the most accurate means of extracting gm, and other methods are described in [5]. It did however prove to be accurate enough for these small devices, and the gm vs. Vgs is shown in figure 5, as well as the 6th order polynomial fit. From the curve fit, the first order transconductance coefficient gm1 is found, along with higher-order gm coefficients. In order to satisfy the gain goal of table 1, equation 4 is used to estimate the number of stages, where n=# of devices and gm is the first order transconductance. It should be noted that equation 4 assumes both the gate and drain lines are of the same impedance. A more general formula for gain is found in [2]. The TQP13 data-sheet specifies a maximum transconductance of 0.75 S/mm, and utilizing this as well as the extracted transconductance yielded two gain estimates, roughly 3dB apart, for n=4. Resulting gain estimates are shown in table 2. While the both the extracted and process specified gm may yield optimistic gain estimates, there is 1.5dB of design margin at choosing n=4 and considering that the device size gives nearly 5Ghz of margin on the cutoff frequency, where gain will likely roll off as frequency increases, it is assumed that this is a good starting point for simulation.

$$G_{dB} = 10 * \log_{10} \left( \frac{Z_O \cdot n \cdot gm}{2} \right) \tag{4}$$

Figure 5: Transconductance, gm, and polynomial curve fit.

| Parameter | Units      | Extracted | Process |

|-----------|------------|-----------|---------|

| n         |            | 4         | 4       |

| Zo        | $[\Omega]$ | 50        | 50      |

| gm        | [S]        | 0.1669    | 0.09    |

| G         | [dB]       | 12.2      | 9.5     |

Table 2: Gain estimates for n=4 of 120um devices for both the extracted 1st order transconductance and the process data-sheet specified transconductance.

#### 4 Simulations

#### 4.1 Ideal Simulation

Utilizing a 120um device, Cgs and Cds were extracted from a linear simulation, as shown in figure 6. Note that Cgs is relatively flat versus frequency which is beneficial given that this is the dominant parameter in terms of frequency cutoff. Inductance values are calculated for a t-line of characteristic impedance of  $Z_O = 50\Omega$ , by considering the t-network topology of figure 2, and  $L_g = Z_O^2 \cdot C_{gs}$  for Cgs of approximately 0.25pF. The resulting gate and drain inductances required for the gate and drain transmission line synthesis are shown in table 3. Note that for some designs the time delay per t-line segment,  $\tau = 1/\sqrt{LC}$ , may prove critical, in particular matching the sub-segment delays on the input and output transmission lines. However, for this design, strict adherence was not found to be super critical.

Figure 6: Cgs and Cds vs. frequency of 120um device

| freq [GHz] | $L_g[\mathrm{nH}]$ | $L_d[\mathrm{nH}]$ |

|------------|--------------------|--------------------|

| 2          | 0.620              | 0.4                |

| 11         | 0.623              | 0.3                |

| 20         | 0.628              | 0.2                |

Table 3: Gate and drain transmission line inductance lumped element values

With the device input and output T-networks defined, the ideal schematic of figure 7 was simulated to verify gain, match, and bandwidth, shown in figure 8. Gain and bandwidth showed good starting performance, while return losses showed some improvement would be necessary.

Figure 7: Ideal Distributed Amplifier Schematic

Figure 8: Ideal Distributed Amplifier Simulation Results

#### 4.2 Detailed Simulation

#### 4.2.1 Linear

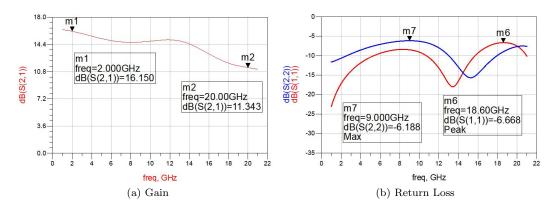

The final distributed amplifier utilized transmission line elements to realize the necessary inductances. The final schematic is shown in section 5, figure 13. To overcome some dc resistance in the drain t-line, the final drain voltage is Vdrain=3.3V, and due to low current draw the gate supply remained at Vgs=0.25V. Final linear performance to 20GHz is shown in figure 9 and to 50GHz in figure 10.

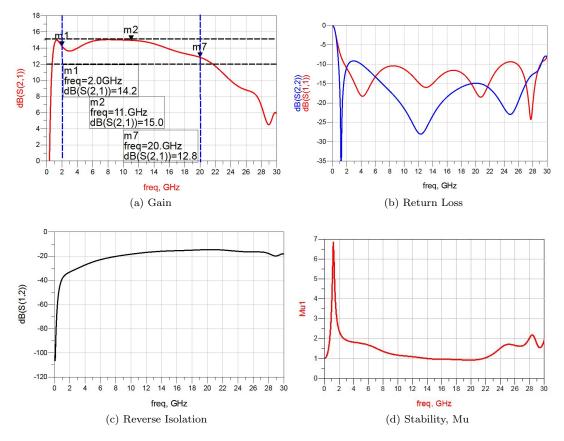

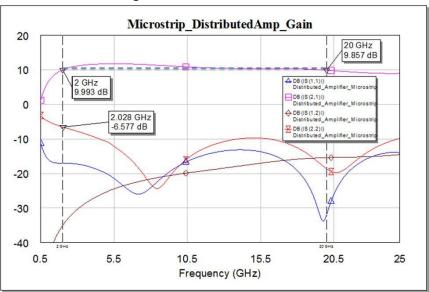

Figure 9: Distributed Amplifier Performance, to 20GHz

Figure 10: Distributed Amplifier Performance, wide-band

#### 4.2.2 Nonlinear

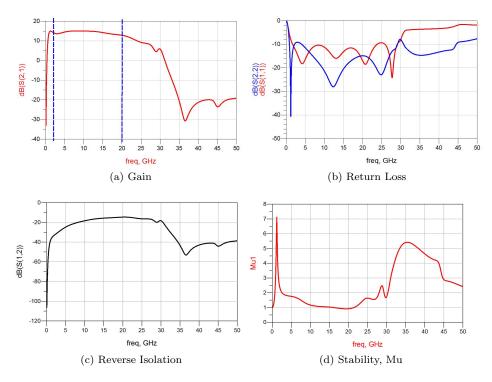

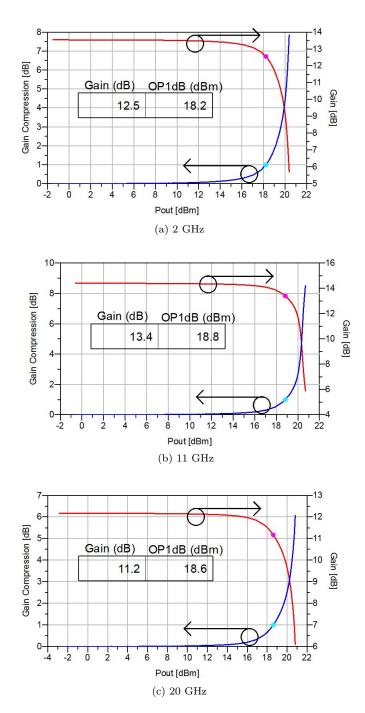

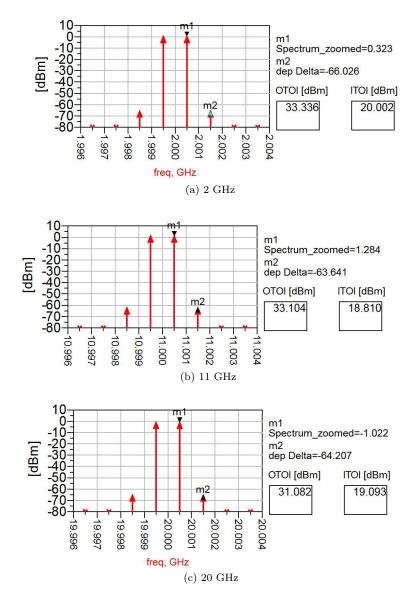

The final design was characterized in simulation for compression and linearity. Compression characteristics and third-order intercept (TOI) at 2, 11, an 20 GHz are shown in figures 11 and 12, respectively.

Figure 11: Gain compression and OP1dB

Figure 12: Third-Order Intercept

# 5 Schematic

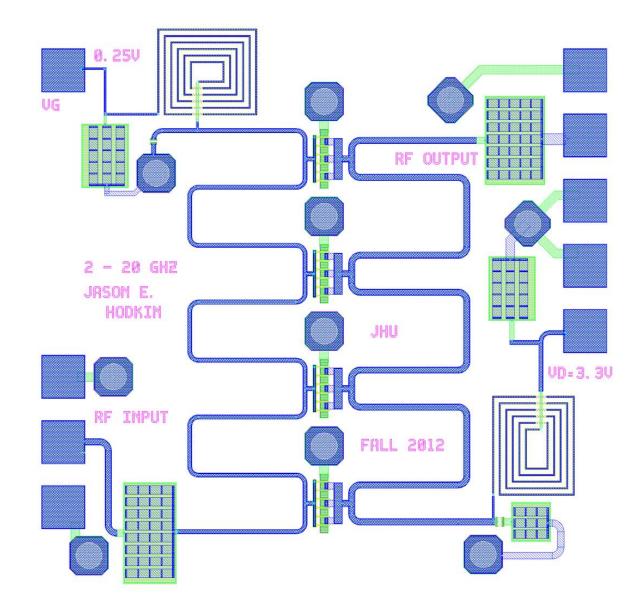

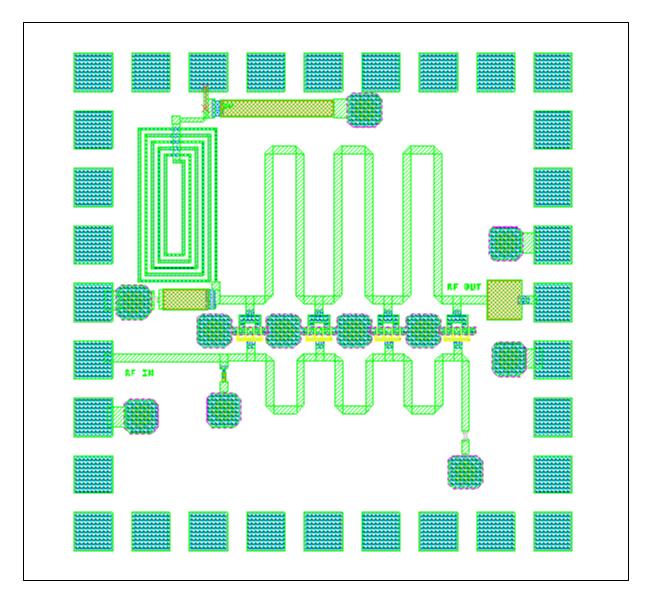

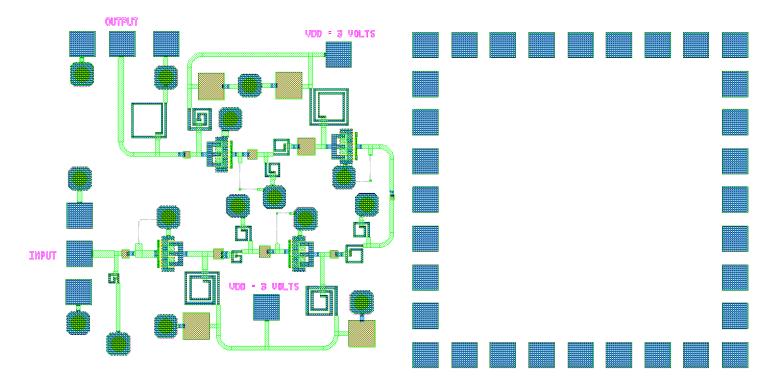

Figure 13: Final 2-20GHz Distributed Amplifier MMIC Schematic

6 Layout

Figure 14: Final 2-20GHz Distributed Amplifier MMIC Layout (ADS Layout)

#### 7 Test Plan

#### 7.1 Linear

Linear s-parameters will be extracted via vector network analyzer (VNA) measurement with calibrated G-S-G probes to 26GHz.

1. Calibrate VNA using probe calibration substrate, 1 to 26 GHz, 1601 points. Port 1 power level should be around -20 dBm.

2. Apply -0.5V to Vgate with needle probe for pinch-off.

3. Apply 3.3V to Vdrain, supply current should be << 1mA.

4. Slowly increase V gate to +0.25 V, or until drain supply current reaches around 113 mA.

5. Acquire 2-port data.

#### 7.2 Nonlinear

Two tests should obtain verification of TOI and compression characteristics.

TOI: two signal generators, 2-way combiner, and a spectrum analyzer are required. For fc= 2, 11, and 20 GHz, fspace=1MHz:

1. Set one signal generator to f1=fc-fspace/2 and the other to f2=fc+fspace/2, set each to around -10 dBm, turn RF off, and connect to combiner inputs.

2. Connect combiner output to device RF input probe, connect RF output probe to spectrum analyzer.

3. Apply dc as described in linear measurement section above.

4. Turn generator RF on.

5. Use makers on SA to extract all f1, f2, 2f1-f2, and 2f2-f1 tone levels in dBm.

6. For each high and low-side fundamental and intermod, find IMD3=dBm(2f-f)-dBm(f), result in dBc.

7. OTOI=Ptones-IMD3/2, where Ptones=output fundamental power in dBm.

Compression: one signal generator and one calibrated RF power meter are required. For fc = 2, 11, and 20 GHz:

1. Connect disabled signal generator to device RF input.

2. Connect device output to power meter

3. Apply dc as described in linear measurement section above.

4. Set each sig gen and power meter to fc.

5. Step sig gen power level from -30 to 10 dBm and acquire in/out levels at 0.5 or 1dB steps.

6. Plot Pout versus Pin, also calculate Gain=Pout-Pin and plot versus Pout to show gain compression.

#### 8 Summary & Conclusions

Final performance relative to goals is summarized in table 4. A moderate gain, general purpose, wide-band amplifier in a compact layout has been designed, simulated, and readied for foundry fabrication. Upon delivery from fab, testing will ensue according to the test plan, and results compared to simulation.

| Parameter                          | Units    | Goals     | Full Band | 2GHz  | 11GHz | 20GHz |                    |

|------------------------------------|----------|-----------|-----------|-------|-------|-------|--------------------|

| Gain                               | [dB]     | > 8       | > 12.8    | 14.2  | 14.9  | 12.8  | small signal       |

| Gain Flatness                      | [dB]     | $\pm 1.5$ | 2         | -     | -     | -     |                    |

| Return Loss, in or out             | [dB]     | > 8       | >9.3      | -     | -     | -     |                    |

| OTOI                               | [dBm]    | > 30      | $\geq 31$ | 33.3  | 33.1  | 31.0  |                    |

| OP1dB                              | [dBm]    | > 17      | > 18      | 18.2  | 18.8  | 18.6  |                    |

| *Pdc                               | [W]      | -         |           | 0.376 |       |       |                    |

| ηdc                                | [%]      | -         |           | 17.5  |       |       | @P1dB              |

| PAE                                | [%]      | -         |           | 16.7  |       |       | $=\eta dc (1-1/G)$ |

| Chip Size                          | $[mm^2]$ | 1.5 x 1.5 | 1.3x1.3   | -     | -     | -     |                    |

| *Vd=3.3V @ 113mA, Vg=0.25 @ 11.6mA |          |           |           |       |       |       |                    |

Table 4: Performance Summary

#### References

- W. S. Percival, "Thermionic valve circuits," British Patent Specification No. 460562, 1937.

- [2] E. Ginzton, W. Hewlett, J. Jasberg, and J. Noe, "Distributed amplification," Proceedings of the IRE, vol. 36, pp. 956 – 969, aug. 1948.

- [3] I. D. Robertson, MMIC DESIGN. London: IEE, 1995.

- [4] C. Campbell, A. Balistreri, M. Kao, D. Dumka, and J. Hitt, "Gan takes the lead," *Microwave Magazine*, *IEEE*, vol. 13, pp. 44–53, sept.-oct. 2012.

- [5] S. A. Mass, Nonlinear Microwave and RF Circuits. Norwood, MA: Artech House, 2nd ed., 2003.

12/13/2012

# 2-20 GHz Distributed PA

Design, Simulation, and Test Plan

Shannon Marshall

# Contents

| Contents                              | iii |

|---------------------------------------|-----|

| Figures                               | iii |

| Abstract                              | 0   |

| Introduction                          | 0   |

| Design Approach                       | 1   |

| Simulations                           | 1   |

| Schematic                             | 2   |

| Layout                                | 5   |

| Test Plan                             | 6   |

| DC & S Parameters                     | 6   |

| Power and Current at 1 dB Compression | 6   |

| Summary and Conclusions               | 7   |

| References                            | 8   |

# Figures

| Figure 1 - Distributed Amplifier Architecture          | 0 |

|--------------------------------------------------------|---|

| Figure 2 - Amplifier Gain                              | 1 |

| Figure 3 - Amplifier Isolation                         |   |

| Figure 4 - Amplifier Input Return Loss                 |   |

| Figure 5 - Amplifier Output Return Loss                |   |

| Figure 6 - Amplifier Stability Factor                  |   |

| Figure 7 - Amplifier Output Power at 1 dB Compression  | 1 |

| Figure 8 - Amplifier Drain Current at 1 dB Compression | 1 |

| Figure 9 - Simplified Amplifier RF Schematic           | 2 |

| Figure 10 - Amplifier RF Schematic Detail              |   |

| Figure 11 - Amplifier DC Schematic                     |   |

| Figure 12 - Amplifier Layout                           |   |

|                                                        |   |

# 2-20 GHz Distributed PA

Design, Simulation, and Test Plan

## Abstract

This paper describes the design of a five-stage distributed power amplifier intended for operation between 2 GHz and 20 GHz. The amplifier design presented is based on the architecture depicted in Figure 1 (Mikemoral, 2012), and achieved greater than +23 dBm output power across the operating frequency band with reasonable input and output return loss.

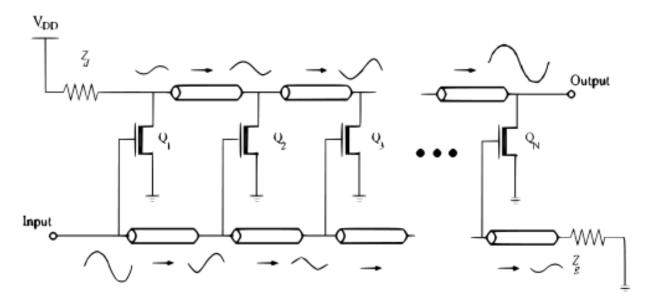

Figure 1 - Distributed Amplifier Architecture<sup>i</sup>

## Introduction

The design presented in this paper attempts to achieve modest RF power output from a distributed amplifier architecture. Performance targets were set by the specifications of the TriQuint TGA8334-SCC power amplifier, which it is intended to replace. The design went through several iterations, which are briefly outlined in the "Design Approach" section of the paper. Linear and nonlinear simulations of the final MMIC showed promising results; a test plan to verify RF performance is outlined in the "Test Plan" section.

# Design Approach

The design goals for this amplifier are taken from the TriQuint TGA8334-SCC datasheet (TriQuint Semiconductor, 2003), and are as follows:

- 2 GHz 20 GHz operating bandwidth

- 0.4 W output power at midband (i.e., +26 dBm)

- On-chip DC blocking capacitors

- 8dB gain +/- 1dB

- -10.8 dB input return loss and -17.7 dB output return loss at midband (1.8:1 input and 1.3:1 output SWR)

- <440 mA drain current draw

To maximize achievable power output, 9V drain bias was selected. +0.35V gate bias yielded a load line with acceptable dynamic range.

The bandwidth of a distributed amplifier is governed by the parasitic capacitance of its transistors, which places an upper limit on the bandwidth of the synthetic transmission line sections.

$$F_{cutoff} = \frac{1}{\pi * Z_0 * C_{gs}} \qquad \qquad F_{cutoff} = \frac{1}{\pi * Z_0 * C_{ds}}$$

Several transistor configurations were simulated to approximate parasitic capacitances; the results appear in Table 1 - parasitic capacitances and cutoff frequencies. The row labeled CASCODE denotes values derived from a cascode arrangement of two n=2,  $W=50\mu m$  PHEMTs.

| Vd      | Vg   | n | W   | Cgs   | Rgs  | Rd  | Rds   | Cds   | G20ghz | Fc       |

|---------|------|---|-----|-------|------|-----|-------|-------|--------|----------|

| 2.8     | 0.6  | 2 | 50  | 0.18  | 14   | 30  | 360   | 0.17  | 11.3   | 3.54E+10 |

| 9       | 0.35 | 2 | 50  | 0.17  | 19.8 | 20  | 385   | 0.2   | 10.91  | 3.18E+10 |

| 9       | 0.35 | 4 | 25  | 0.17  | 18   | 20  | 385   | 0.195 | 8.46   | 3.26E+10 |

| 9       | 0.35 | 4 | 50  | 0.51  | 11   | 11  | 197.5 | 0.67  | 9      | 9.50E+09 |

| 9       | 0.35 | 6 | 50  | 0.975 | 7.7  | 7.8 | 130   | 1.4   | 6.8    | 4.55E+09 |

| 9       | 0.35 | 2 | 100 | 0.51  | 15   | 11  | 197.5 | 0.7   | 8.52   | 9.09E+09 |

| 9       | 0.35 | 4 | 100 | 1.524 | 7.9  | 6   | 98    | 2.5   | 4.65   | 2.55E+09 |

| CASCODE |      |   |     | 0.127 | 10.1 | 3   | 3000  | 0.047 | 9.41   | 5.01E+10 |

**Table 1 - Parasitic Capacitances and Cutoff Frequencies**

Of the simulated transistors, the n=2,  $W=50\mu m$  PHEMTs at +0.35V gate bias and +9V drain bias yielded the best combination of cutoff frequency and gain at 20 GHz.

Multiple topologies were evaluated to attempt to balance gain, stability, and output power. Preliminary simulations with ideal circuit elements were performed on the following circuits:

- 3-transistor distributed amplifier (Pout too low)

- 4-transistor distributed amplifier (Pout too low, difficult to stabilize)

- 5-transistor distributed amplifier (Pout too low, difficult to stabilize)

- 5-transistor distributed amplifier with capacitor-coupled gate (Robertson, 5.10.4: High Power Distributed Amplifiers, 2001) (P<sub>out</sub> too low)

- 3-transistor-pair cascode distributed amplifier (Robertson, 5.8: Distributed amplifier, 2001) (P<sub>out</sub> too low)

- 4-transistor-pair cascode distributed amplifier (Pout too low, difficult to stabilize)

- 5-transistor distributed amplifier with capacitor-coupled gate and n=4 W=50 µm output transistors (Robertson, 5.10.4: High Power Distributed Amplifiers, 2001)

The capacitor-coupled gate amplifier design afforded two advantages over the other topologies: the output power was higher than the other amplifiers, and the gate capacitors afforded a way to trade off circuit bandwidth and gain against overall stability. The 5-transistor capacitor-coupled gate amplifier with n=4, W= 50  $\mu$ m output transistors shown in Figure 9 - Simplified Amplifier RF Schematic was therefore selected.

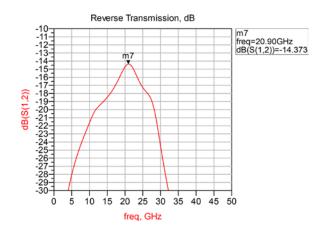

Nominal inductor values for this circuit were  $L_D=0.5$  nH and  $L_G=0.425$  nH. After tuning the inductor values to give the best overall performance, linear simulation was used to select TQP13 MLIN lengths of desired shape and equivalent inductance. The inductance wasn't varied for the output stages; this detuning maintained the amplifier bandwidth at the cost of return loss.

## Simulations

Linear simulations using TriQuint device models indicate acceptable forward and reverse transmission over the designed operating band; results are shown in Figure 2 - Amplifier Gain and Figure 3 - Amplifier Isolation.

Figure 2 - Amplifier Gain

Figure 3 - Amplifier Isolation

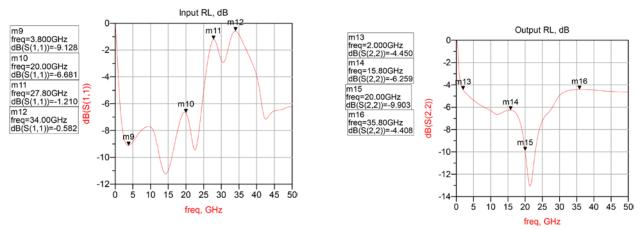

Input return loss, shown in Figure 4 - Amplifier Input Return Loss, is better than -6 dB over the operating frequency band; output return loss, shown in Figure 5 - Amplifier Output Return Loss, is better than -4 dB over the operating band.

Figure 4 - Amplifier Input Return Loss

**Figure 5 - Amplifier Output Return Loss**

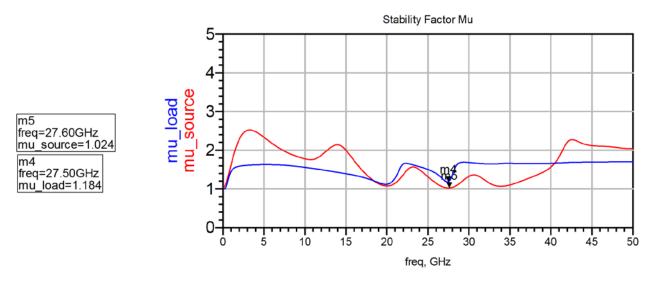

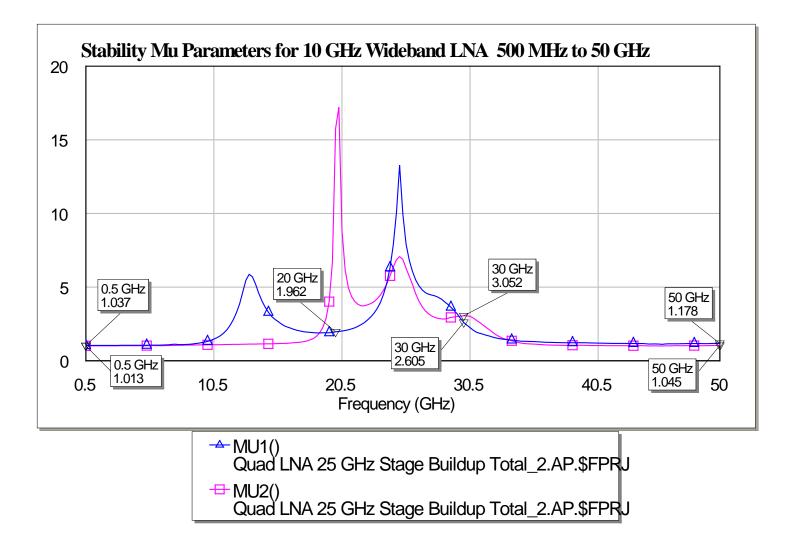

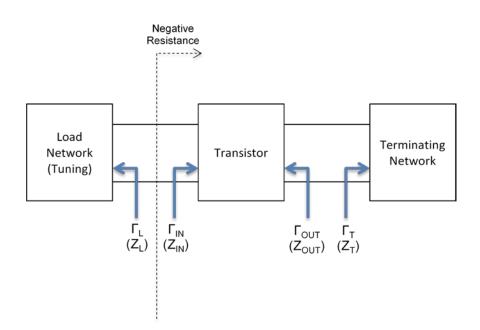

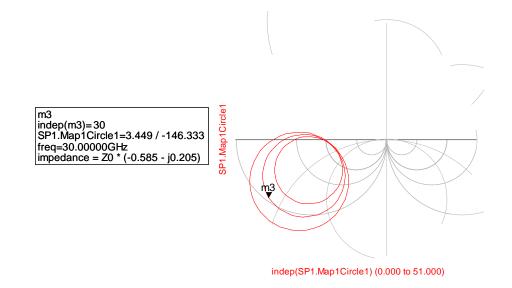

The amplifier's stability parameter,  $\mu$ , is >1 over the simulated frequency range of 0.5 GHz – 50 GHz; the amplifier should be unconditionally stable between those frequencies.

#### Figure 6 - Amplifier Stability Factor

Linear DC simulation predicts a drain current draw of 292 mA and a gate current draw of 57 nA in linear operation.

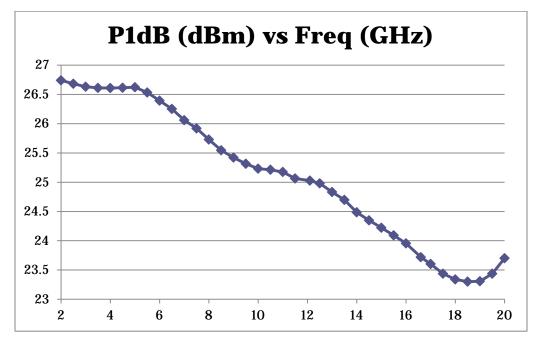

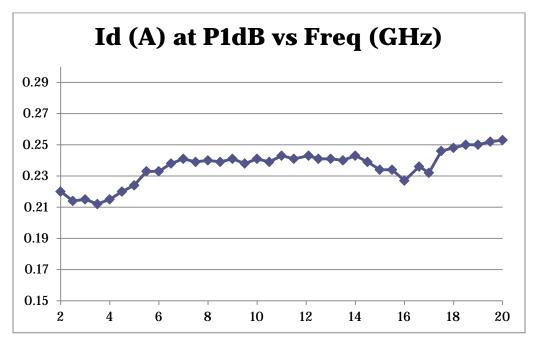

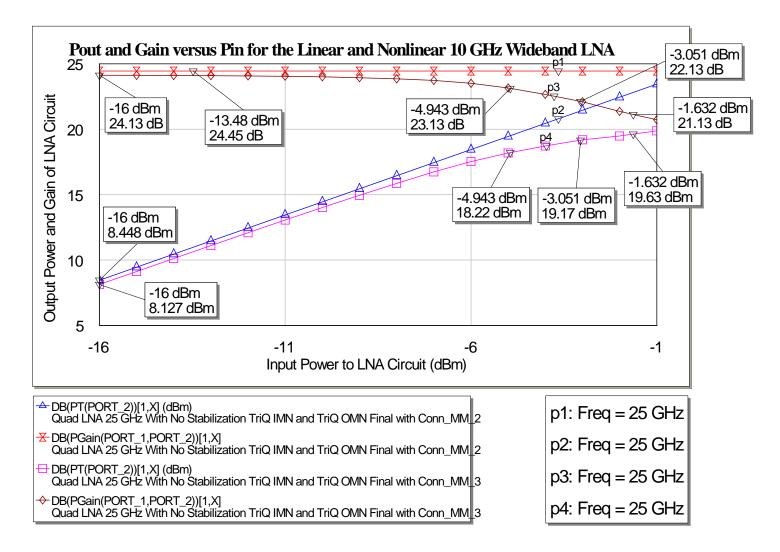

P1dB is greater than +23 dBm over the frequency band, and greater than +26 dBm from 500 MHz -7 GHz, according to harmonic balance nonlinear simulation. Drain current in compression should be around 240 mA over most of the frequency band, exceeding 250 mA above 18 GHz.

Figure 7 - Amplifier Output Power at 1 dB Compression

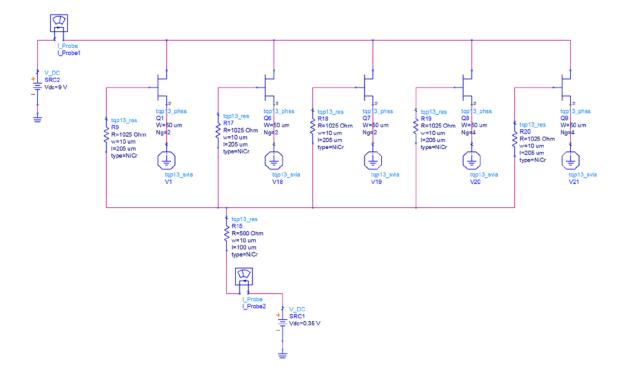

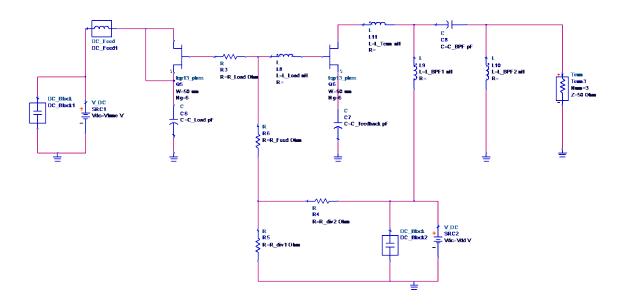

# Schematic

A simplified RF schematic of the final distributed amplifier design is presented in Figure 9 - Simplified Amplifier RF Schematic. Drain and gate inductors were realized on-chip with TQP13 MLIN elements. The first two stages have two coupling capacitors because the capacitance required for stability was too low to be realized with a single standard capacitor element. The fourth and fifth transistors (next-rightmost and rightmost on the below schematic) have four 50- $\mu$ m gate elements; the first, second, and third have two 50- $\mu$ m gate elements.

**Figure 9 - Simplified Amplifier RF Schematic**

Figure 10 - Amplifier RF Schematic Detail

The DC circuit is shown in Figure 11 - Amplifier DC Schematic. The circuit runs at a 9V drain bias and a +0.35V gate bias.

**Figure 11** - Amplifier DC Schematic

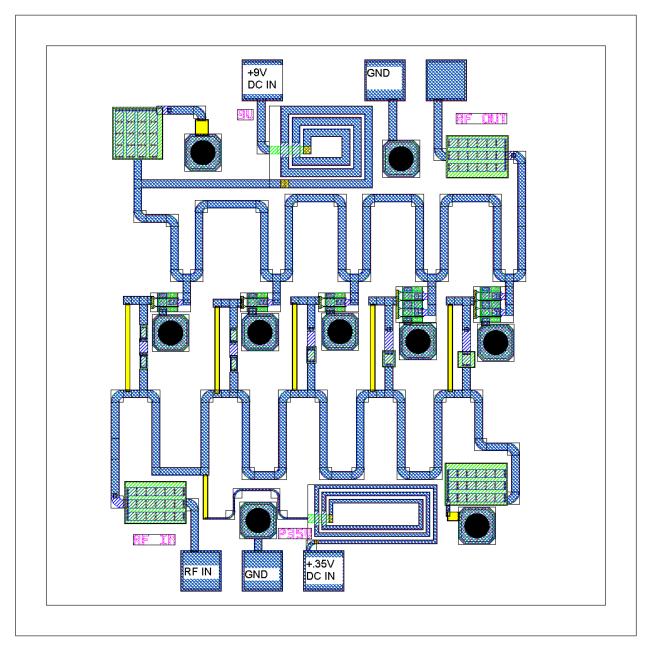

# Layout

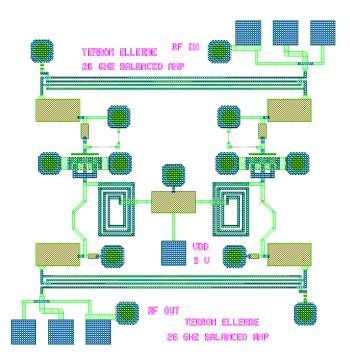

The final layout of the MMIC appears in Figure 12 - Amplifier Layout. The  $50\Omega$  drain termination resistor is on the chip (whereas the TGA8334-SCC required an off-chip termination resistor). Gate and Drain decoupling capacitors and inductors are likewise on the MMIC.

Figure 12 - Amplifier Layout

# Test Plan

### **DC & S Parameters**

S parameter measurement will be performed using a VNA and a pair of RF signal probes calibrated over the operating band of 2 GHz – 20 GHz.

- 1. Calibrate VNA from at least 2 GHz 20 GHz, with at least 181 points (to measure every 100 MHz).

- 2. Apply -0.5V to the gate DC input through a needle probe to hold the amplifier in pinch-off.

- 3. Apply +9V to the drain through a second needle probe, ramping up from OV. Watch for excessive current draw.

- 4. Slowly increase gate DC input to +0.35V. Amplifier should be drawing < 300 mA. Record gate and drain currents.

- 5. Measure s parameters.

### Power and Current at 1 dB Compression

Compressed power will be measured at frequencies of interest: 2 GHz, 11 GHz, 18.5 GHz, and 20 GHz. This measurement requires a signal generator, an attenuator (since the maximum output power is higher than the "Do Not Exceed" power on most power heads), and a power meter.

- 1. Connect signal generator to RF IN port; make sure RF output of signal generator is OFF.

- 2. Connect device output to power meter through a suitable attenuator. 10 dB probably allows a good safety margin.

- 3. Apply DC per steps 2-4 of the DC & S Parameters section of the test plan.

- 4. Set signal generator and power meter to the frequency of interest.

- 5. Take a linear measurement at -20 dBm input power, and increase in large (3 6 dB) steps until Pout is around +10 dBm. Increase in smaller steps (1 dB or 0.5 dB) until gain is 1 dB compressed relative to linear gain measurement.

- 6. Record all Pin and Pout measurements, along with gate and drain current at linear measurement point and at compressed measurement point.

# Summary and Conclusions

Amplifier performance is compared to design goals in Table 2 - Amplifier Performance vs. Goals. The design falls short of its performance parameters, but still produces respectable output power and flat gain over the entire operating band. Once the amplifier is fabricated, performance can be compared to simulated results and evaluated against specifications.

| Metric                        | Units | Goal  | Performance | Notes                                     |

|-------------------------------|-------|-------|-------------|-------------------------------------------|

| Small Signal Gain             | dB    | > 8   | 7.8         | Worst case performance at 15.8 GHz        |

| Gain Flatness                 | dB    | +/- 1 | +/- 0.6     |                                           |

| Input Return Loss at midband  | dB    | >10.8 | 9           | 6.7 dB worst case at 20 GHz               |

| Output Return Loss at midband | dB    | >17.8 | 6.5         | 4.5 dB worst case at 2 GHz                |

| Output P1dB at midband        | dBm   | > 26  | 25.2        | 26.75 at 2 GHz; 23.3 at 18.5 GHz          |

| DC Power                      | W     |       | 2.28        | 253 mA @ 9V + 0.292 mA @ 0.35V            |

| Drain Current                 | А     |       | 0.253       | At 1 dB compression, worst case at 20 GHz |

| Efficiency                    | %     |       | 10.3        | At 20 GHz. Range from 9.5% to 24.2%       |

Table 2 - Amplifier Performance vs. Goals

## References

Mikemoral. (2012, December 10). *Distributed amplifier*. Retrieved December 2012, 2012, from Wikipedia: http://upload.wikimedia.org/wikipedia/commons/thumb/a/ab/N-stage\_traveling-wave\_amplifier.svg/500px-N-stage\_traveling-wave\_amplifier.svg.png

Robertson, I. D. (2001). 5.10.4: High Power Distributed Amplifiers. In I. D. Robertson (Ed.), *RFIC and MMIC design and technology* (p. 234). London, United Kingdom: Institute of Electronics Engineers.

Robertson, I. D. (2001). 5.8: Distributed amplifier. In I. D. Robertson (Ed.), *RFIC and MMIC design and technology* (pp. 213-225). London, United Kingdom: The Institution of Electrical Engineers.

TriQuint Semiconductor. (2003, April 25). TGA8334-SCC Datasheet. Richardson, Texas, United States of America.

<sup>i</sup> Figure by Wikipedia user <u>Mikemoral</u>, and used under terms of <u>Creative Commons Attribution 3.0</u> <u>Unported</u> license. JOHNS HOPKINS UNIVERSITY

# 2-20 GHz LNA

# EN.525.787 – MMIC Design

Brian Billman 12/13/2012

#### <u>Abstract</u>

This paper describes a 2-20 GHz LNA designed on the Triquint GaAs TQP13 process. The goal was to achieve greater than 10dB gain and less than 3dB noise figure across the entire band. The design meets these goals in simulation.

#### Design Approach

In order to meet the wideband requirements a distributed amplifier topology was implemented for this design. Distributed amplifiers are able to obtain large gain-bandwidth products relative to other topologies. For this design I implemented the distributed topology by connecting the gates and drains of multiple stages of transistors using transmission lines. The inductance of the transmission line is to tune out the capacitance of the transistors. You could also use inductor coils between transistors.

#### Specifications:

Frequency:2-20GHzGain:10dBNoise Figure:3dBStability:Unconditional

My first step was to determine the necessary transistor size and the required number of stages to meet the gain and noise figure requirements. My initial design had 4 stages with 2x20 transistors. The noise figure was well below the spec but I was unable to meet the gain requirement. The performance of my initial design is shown in Figure 1 and Figure 2.

Figure 1. The noise figure of the initial design is well below requirements

Figure 2. The gain of initial design does not meet the requirements

In order to meet the gain requirement I increased the transistor sizes to 4x40. This increased the noise figure slightly however it still met the spec. With the transistor and stages determined, I moved on to tuning the gate and drain lines. It was a challenge to keep the design unconditionally stable while meeting all the requirements. To resolve this I treated the gate and drain resistors as stabilizing components and tuned their values from the original 50 ohms. I ended up with a 25 ohm drain resistor and an 80 ohm gate resistor.

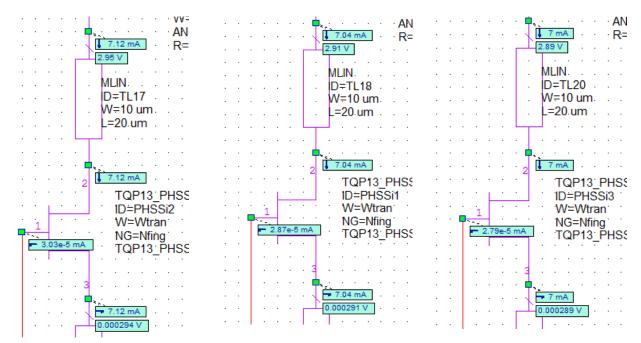

The final step was to add the bias circuit and complete the layout. In order to simplify the design I decided to use a gate voltage of 0V. A 3V drain bias provided the best performance. As shown in Figure 7, this biases each transistor at ~7mA. I added the drain bias pad behind the largest inductor that fit on the layout. This slightly degraded performance.

#### **Simulations**

Figure 3. Linear simulation of final design.

The addition of the bias circuit and changes during final layout slightly affected the gain. At 17GHz the gain dips below the spec to 9.5dB. The gain flatness was 3dB with the highest gain being 12.5dB at 2GHz. The gain roll off at the high end of the band is rather gradual which should help reduce any performance degradation from modeled to measured. The input return loss is below -5dB across the band while the output return loss is mostly below 10dB across the band.

Figure 4. Noise figure simulation of final design.

With the smaller transistors the noise figure was flat around 2dB across the band. With the larger transistors the noise figure pulled up on the ends of the band but was still below the spec. The lowest noise figure is 2dB at 13GHz. The highest noise figure is 2.85dB at 2GHz.

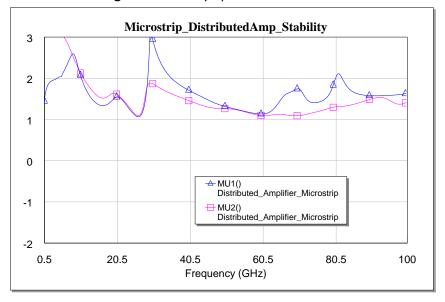

Figure 5. Stability simulation of final design.

The design is unconditionally stable up to 100GHz. This was achieved by tuning the resistors as well as the length and characteristic impedance of the transmission lines.

Figure 6. The DC operating point

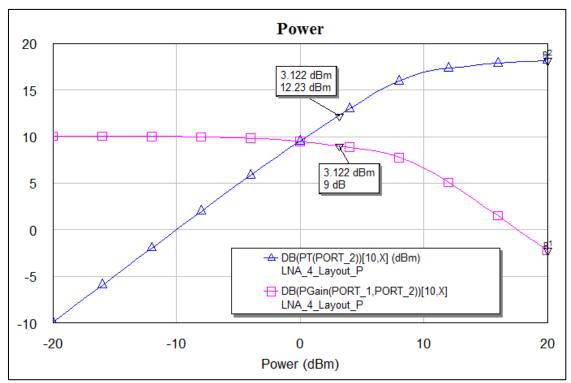

Figure 7. Power with P1dB highlighted

The bias and power simulations are shown in Figure 7 and Figure 8 above. I chose to bias the LNA with OV on the gate and 3V on the drain. This means that each transistor draws ~7mA of current. The 1dB compression point of the LNA is at 12.2 dBm.

### <u>Schematic</u>

Figure 8. Final schematic with interconnects

Figure 9. Final schematic without interconnects

Figure 10. Layout

The design fit well on the given chip size. Given more room, I would be able to increase the bias circuit inductor which would bring the gain back up above 10dB. Adding a second ground via to each transistor helped performance significantly.

#### <u>Test Plan</u>

- 1) Connect power supply to DC pad

- a) Set current limit to 50mA

- b) Set voltage to 3V

- 2) Connect network analyzer to the RF input and output ground-signal-ground pads

- 3) Measure s-parameters of LNA and compare to simulated results

- 4) Connect noise figure source to input probe and noise figure meter to output probe

- 5) Measure NF and compare to simulated results

#### **Conclusion**

The distributed amplifier topology was the natural selection for this LNA design. With this topology I was able to achieve good performance over the required band of 2-20GHz. By adjusting the transistor size I was able to balance the gain and noise figure performance of the circuit. This design meets the noise figure specification of 3dB. It meets the gain requirement of 10dB across most of the band but dips down to 9.5dB at the lowest point. The design is also unconditionally stable.

JOHNS HOPKINS UNIVERSITY ENGINEERING FOR PROFESSIONALS

# Low Noise Amplifier 2-20 GHz

# EN.525.787 MMIC Design

Robert Reyes 12/13/2012

# Contents

| 1 | Cor                                                | ntents                                          | tents1                    |  |  |  |  |  |  |

|---|----------------------------------------------------|-------------------------------------------------|---------------------------|--|--|--|--|--|--|

| 2 | Abs                                                | Abstract2                                       |                           |  |  |  |  |  |  |

| 3 | Introduction2                                      |                                                 |                           |  |  |  |  |  |  |

| 4 | Design Approach2                                   |                                                 |                           |  |  |  |  |  |  |

|   | 4.1                                                | Specifi                                         | ications vs. Goals2       |  |  |  |  |  |  |

|   | 4.2                                                | Trade-                                          | offs2                     |  |  |  |  |  |  |

| 5 | Sim                                                | nulations                                       | 5                         |  |  |  |  |  |  |

|   | 5.1                                                | Linear.                                         |                           |  |  |  |  |  |  |

|   | 5.2                                                | Nonlin                                          | ear5                      |  |  |  |  |  |  |

|   | 5.3                                                | Bias (D                                         | DC Analysis)              |  |  |  |  |  |  |

| 6 | Sch                                                | nematic                                         |                           |  |  |  |  |  |  |

|   | 6.1 Figure I: RF Schematic (without Interconnects) |                                                 |                           |  |  |  |  |  |  |

|   | 6.2                                                | 5.2 Figure J: RF Schematic (with Interconnects) |                           |  |  |  |  |  |  |

| 7 | Lay                                                | out                                             |                           |  |  |  |  |  |  |

| 8 | Tes                                                | st Plan                                         |                           |  |  |  |  |  |  |

|   | 8.1 Equipment                                      |                                                 |                           |  |  |  |  |  |  |

|   | 8.2                                                | .2 Measurements                                 |                           |  |  |  |  |  |  |

|   | 8.2.1 DC Bias                                      |                                                 |                           |  |  |  |  |  |  |

|   | 8.2.2                                              |                                                 | -Parameters11             |  |  |  |  |  |  |

|   | 8.2                                                | .3 N                                            | oise Figure11             |  |  |  |  |  |  |

|   | 8.2                                                | .4 0                                            | utput Power/Compression11 |  |  |  |  |  |  |

| 9 | Cor                                                | nclusion                                        |                           |  |  |  |  |  |  |

### 2 Abstract

The design is a wideband low noise amplifier using the TriQuint 0.13um pHEMT process, fitting on a 60x60mil GaAs chip. The low noise amplifier operates over a 2-20 GHz bandwidth, providing roughly 10dB of gain across the entire band with a low noise figure less than 3dB. The return loss is less than -10dB over the majority of the band.

## **3** Introduction

The low noise amplifier (LNA) is used to amplify weak signals while adding minimal noise to the system. The LNA in this paper was designed to operate over a wide bandwidth (2-20 GHz) with modest gain (~10dB) and a reasonably low noise figure (<3 dB) using the TriQuint 0.13um pHEMT process (TQP-13N). This particular LNA design uses a distributed amplifier approach to achieve the required RF performance over the entire frequency band.

## 4 Design Approach

#### 4.1 Specifications vs. Goals

TriQuint provided the following suggested specifications for a wideband low noise amplifier: 2-20GHz, NF < 3dB, P1dB > 17.5, and variable gain. From these, the following specifications for this design were generated: the low noise amplifier shall operate from 2 to 20 GHz with a gain of approximately 10dB and noise figure less than 3dB. The design shall also use the TriQuint 0.13um pHEMT process. The 1dB compression point of 17.5dBm is considered to be a goal, although the design focus was mainly on achieving the gain and noise figure specifications. Another goal was to make the design stable when looking into a 50-ohm match.

#### 4.2 Trade-offs

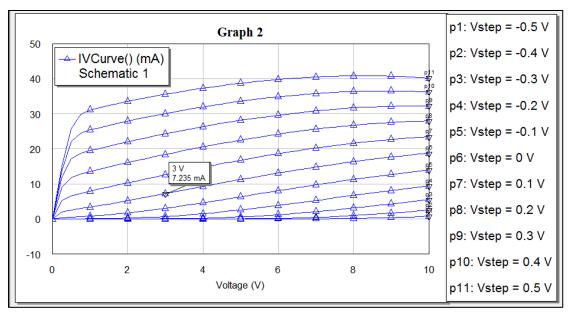

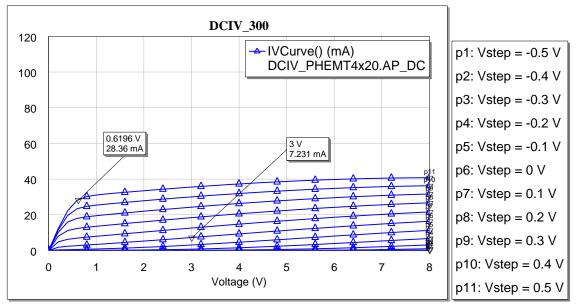

Distributed amplifiers are known for providing relatively flat gain over a large bandwidth. Because this low noise amplifier design had to operate over a wide frequency band, the distributed amplifier architecture was selected as a baseline versus a multi-stage amplifier design. The distributed amplifier template was also selected due to the uniform inductor structure between stages, making it simpler to add or remove stages during the initial design process. The designer started the design with a threestage distributed amplifier architecture and three stages proved to be sufficient to provide the necessary RF performance. Initially, the design used FETs with a 6x50um periphery. This was due to the availability of an S2P file for the 6x50um FET biased at 3V and 30mA; however, it was difficult to stabilize the circuit and achieve gain flatness. Reducing the number of fingers and finger length to a 4x20um periphery, while maintaining a gate voltage of 0V, resulted in a vast improvement in the RF performance of the LNA circuit. Flatter wideband gain was achieved and the circuit became unconditionally stable. Reducing the periphery also reduced the current draw of the device, thereby improving the noise figure of the LNA. The DCIV curve of the 4x20um FET is seen below. At a gate bias of 0V, the device drew a drain current of ~7mA at a drain voltage of 3V.

#### **Figure A:** DCIV Curve for 4x20um pHEMT

Another trade-off is the use of microstrip transmission lines for tuning instead of inductors. In the initial design, ideal inductors were used as a baseline but this gave way to microstrip transmission line. The reason for this switch is that the inductor values proved to be relatively small and microstrip lines would be easier to size/tune to the needed inductance, using the rule of thumb of 1pH/1um of inductance, instead of trying to adjust the spacing and number of turns to size the inductors appropriately. Also, space was not an issue when switching to a microstrip realization of the circuit. If the LNA design had tighter chip size constraints, then using inductors instead would significantly reduce the amount of space used.

## **5** Simulations

#### 5.1 Linear

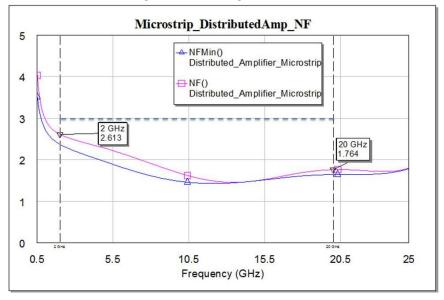

As seen in Figure B, the gain is approximately 10dB across the entire band. The return loss is decent across the majority of the band but it does roll up to roughly -6.5dB at the lower band edge. Figure C shows that the noise figure is well below the specification of less than 3dB. It is much better at the high end of the band than the low end though. Both figures indicate that the design meets both gain and noise figure specifications.

Figure B: S-Parameters for LNA

Figure C: Noise Figure for LNA

One goal for the design was to make the LNA circuit unconditionally stable. There were issues achieving this when initially designing with the 6x50um FET sizes, but after switching to the 4x20um periphery, the design became unconditionally stable. The design's stability is seen in Figure D, where the stability factor is shown to be greater than 1 up to 100GHz.

Figure D: Stability up to 100GHz for LNA

#### 5.2 Nonlinear

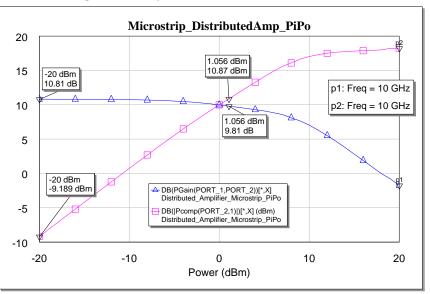

One of the goals listed by TriQuint was to achieve a P1dB of 17.5dBm; however, this particular goal was not worked towards. As seen in Figure E, the 1dB compression point, at 10GHz, was found to be 10.87dBm at 1.056dBm in. Figure G shows the family of compression and gain curves from 2 to 20GHz at 1GHz steps. The saturated power appears to be around 18dBm, as seen in Figure G.

Figure F: Output Power versus Input Power for LNA

Figure G: Output Power versus Frequency for LNA

## 5.3 Bias (DC Analysis)

The DCIV curves for the TOM4 pHEMT model for the 4x20um FET size indicated that a 3V drain voltage with a 0V gate bias would draw approximately 7mA of current. Figure H below shows the DC simulation results at each stage in the distributed amplifier circuit. The simulated current draw corresponds to the DCIV curve seen in Figure A. The total drain current is, as such, expected to be roughly 21mA.

#### Figure H: Drain Current and Voltage Draw Per Stage

# 6 Schematic

# 6.1 Figure I: RF Schematic (without Interconnects)

# 6.2 Figure J: RF Schematic (with Interconnects)

9

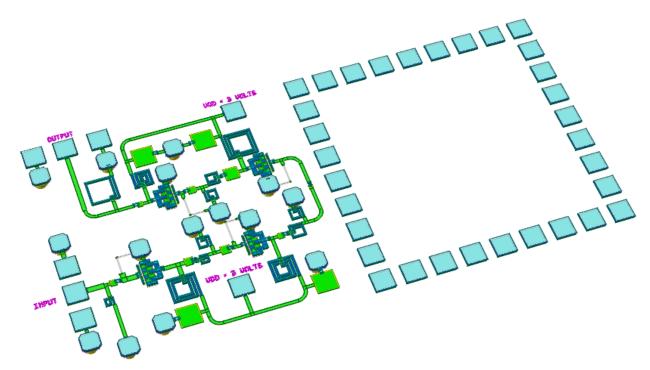

# 7 Layout

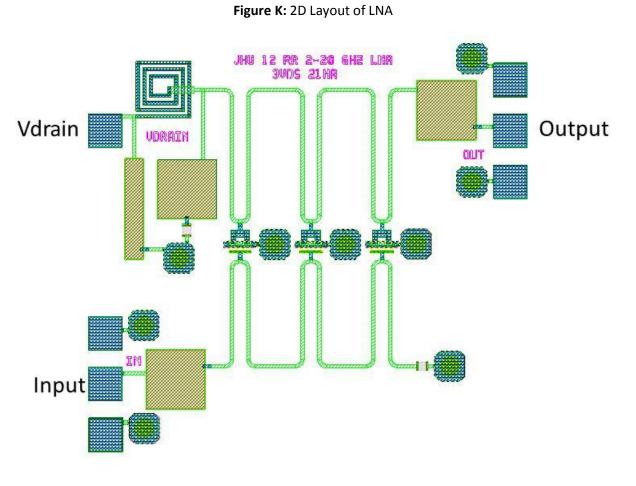

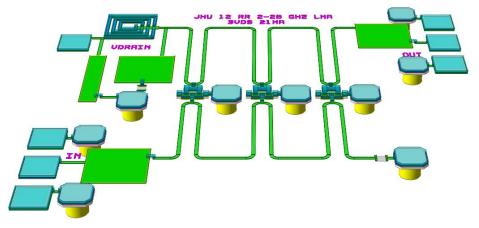

Figure L: 3D Layout of LNA

# 8 Test Plan

### 8.1 Equipment

For measuring the RF performance of the LNA, the following equipment is needed:

- DC power supply

- network analyzer, such as the Agilent 8510 or PNA

- RF signal generator

- spectrum analyzer or power meter

- noise figure analyzer

#### 8.2 Measurements

#### 8.2.1 DC Bias

- 1. Connect power supply to drain voltage pad.

- 2. Set power supply current limit to 30mA. According to the DC simulation, 21mA should be the expected current draw.

- 3. Set voltage to 3V. Turn power supply on to turn on low noise amplifier circuit.

#### 8.2.2 S-Parameters

- 1. Connect Port 1 of Network Analyzer to pad labeled "In" and Port 2 to pad labeled "Out".

- 2. Set frequency range from 1 to 21 GHz and input power level to -20dBm.

- 3. Measure S11, S12, S21, and S22 of the device. The expected gain (S21) is 10dB across 2 to 20 GHz with a return loss of roughly -10dB across the majority of the band.

#### 8.2.3 Noise Figure

- 1. Connect circuit to a noise figure analyzer.

- 2. Measure noise figure from 1 to 21 GHz.

#### 8.2.4 Output Power/Compression

- 1. Connect output of RF signal generator to the input of the LNA. Connect power meter or spectrum analyzer to the output of the LNA.

- 2. Beginning at -10dBm, measure the output power at 1dBm steps up to 10dBm, from 2-20GHz in 4GHz steps. Expected P1dB point at 10GHz is 10.8dBm out at 1dBm in.

# 9 Conclusion

For this design, it was shown that a low noise figure and modest gain is achievable for a wideband low noise amplifier. This was obtained by using a distributed amplifier architecture, which is known for its wideband applications. With a three-stage distributed amplifier circuit using 4x20um transistors, the design was able to meet the specifications of 10dB gain and less than 3dB noise figure from 2 to 20GHz. The gain was also decently flat across the band of interest. In simulation, the circuit was shown to be unconditionally stable up to 100GHz. The P1dB point was found to be approximately 11dBm and the saturated power was roughly 18dBm, according to the nonlinear simulation. One improvement for the design would be to convert the microstrip lines, which were used for tuning, to inductors in order to save space. Overall, however, the low noise amplifier design was successful in meetings the specifications.

Wideband LNA 5-15 GHz

Designed by Michael Coon

For JHU EP class EN525.787 MMIC Design

#### ABSTRACT:

The purpose of this design was to see just how wideband one could make an LNA using TriQuint's MMIC fabrication process and more traditional amplifier design, rather than a distributed amplifier design. The requirements used to guide the design were those of one of TriQuint's old wideband LNA designs. While the design did not meet the bandwidth requirement of 2-20 GHz, it did get fairly close, while maintaining more than enough gain and noise figure performance.

#### **INTRODUCTION:**

Low Noise Amplifiers are used as the first component in a receiver chain to set up the noise performance for the rest of the system and provide some gain to the weak signal coming into the system. For this purpose, an older MESFET design by TriQuint had a bandwidth of 2-20 GHz, with a gain of at least 10 dB and a noise figure of less than 3 dB throughout the band. In the pictures of the circuit it appeared that this performance was obtained using a distributed amplifier setup. Since the new pHEMTs have a larger operational bandwidth, I decided to see just how far I could push the bandwidth of a more traditional 2 stage LNA design.

In forgoing the distributed amplifier design, I realized that I would be making several trade offs that would affect performance, both negatively and positively. First, I realized that the bandwidth would probably not be able to match that of a distributed amplifier. My design only has two stages, and each individual stage would not be nearly enough to get the full range of a distributed amplifier, however I was hoping that the next trade off would make up for that. The second trade off being gain. It was my hope that by doing a design in which I am directly matching one stage to get gain, that I would be able to exceed the overall gain of a distributed amplifier. The only thing I was not aware of is how much my noise figure would be affected by going with a two stage amplifier design. Though it was my hope that I would be able to get a slightly better noise figure than with the distributed amplifier.

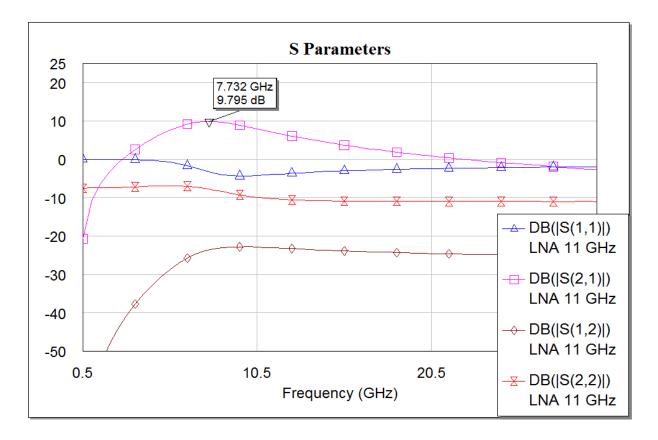

#### DESIGN PROCESS:

For the design process, I designed each of the two stages differently. The first stage was designed at 11 GHz to be a textbook LNA with some noise figure traded off to get more gain. This lead to the following linear S-parameter simulation shown on the next page. It is worthwhile to note that the gain is not at a maximum at 11 GHz due to the trade off between gain and noise figure. The noise figure of the circuit (not shown) was about 1.335 at 11 GHz and stays below 3 dB from 3.5 GHz up to at least 30 GHz which was a fairly promising start.

Next, in order to bring up the gain throughout the band of interest, I designed a conjugate matched amplifier at 14 GHz. The goal here was to take the gain that is already present and close to what is required, and boost the areas that were not high enough. Fourteen gigahertz seemed like a fairly good point to do this between the first stage was designed at 11 GHz and had a gain maximum at 7.7 GHz, so for the most part the lower frequencies were fairly well off. From there, the circuit was combined into a two stage amplifier and some work was done to keep the amplifier stable. The following page shows the resulting S-parameters and noise figure.

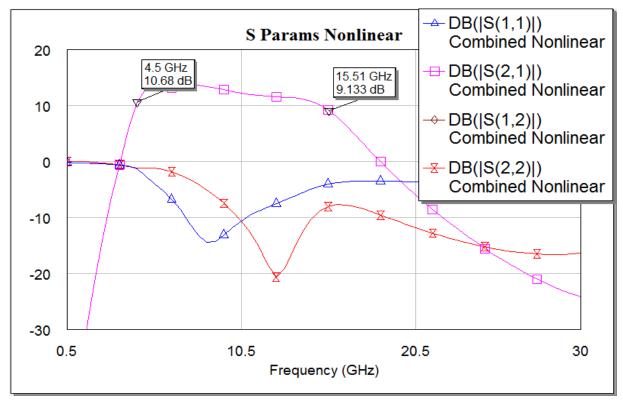

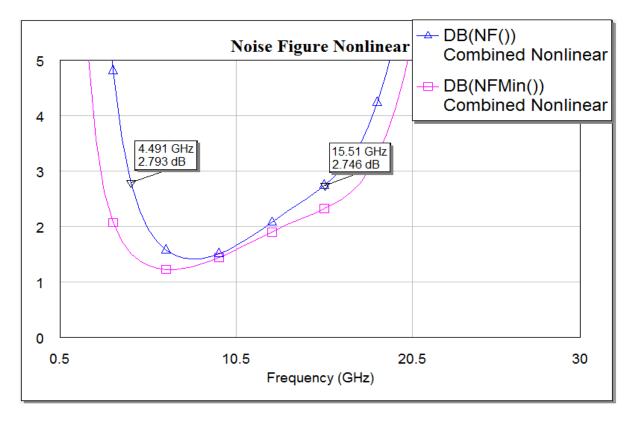

As can be seen, the gain was above the requirement from 5.45 GHz and 15.76 GHz however the noise figure was a bit high. These simulations were done with an S-parameter file instead of a pHEMT model, so I assumed that performance would change with the non-linear model and proceeded.

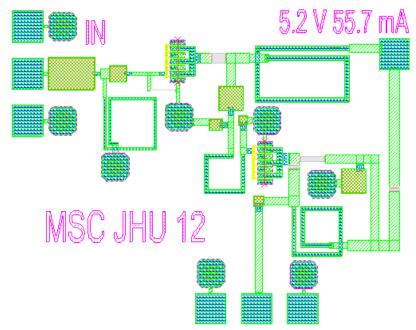

In order to choose a bias point for the design, I tried to mimic that of the S-parameter file for the LNA portion of the design which lead to a voltage of about 5.2 V due to my stabilizing resistor being in series. This is a happy coincidence since it is fairly close to TTL voltage levels meaning it could be used near or in conjunction with digital circuitry with a small performance hit. The results of non-linear simulation are shown below.

The change in the shape of S21 is due to the addition of interconnects to the circuit. As can be seen, over a reasonable range from 4.5 GHz to 15 GHz, the gain is above 10 dB and the noise figure is less than 3 dB. Return loss is also fairly good in place with S22 measuring -20 dB at 12.5 GHz and S11 measuring -14.5 at 8.5 GHz. The following is a schematic level view of the amplifier without connections between the parts.

The finished layout is shown below:

For probing purposes, this circuit has ground signal ground connections, however in a packaged design, it would not. The lettering is not the finished labeling as the font used would not pass design rule checking.

# TEST PLAN:

- 1) Hook up ground signal ground probes to the proper terminals as shown in the design.

- 2) Attach DC probe to the labeled test point.

- 3) Apply 5.2 V to LNA

- 4) Check current. If current is much greater or much less than 55.7 mA cease testing.

- 5) Use Network analyzer to gather S-parameters over entire frequency range

- 6) Use noise figure measurement equipment to gather noise figure data for entire frequency range.

- 7) Write down results and compare.

## CONCLUSIONS:

I conclude that it is possible to make a fairly wideband LNA using traditional amplifier design techniques as opposed to doing a distributed amplifier design. That being said, the bandwidth will never be as large as a distributed amplifier, but the gain and noise figure can be comparable over a range of frequencies at less current draw. Therefore, such a design would be more appropriate for a battery powered or space flight project over a distributed amplifier design that would have several more transistors.

# DESIGN OF A LOW-NOISE AMPLIFIER FOR THE FREQUENCY RANGE 20 GHz to 30 GHz By JOHN NOVAK

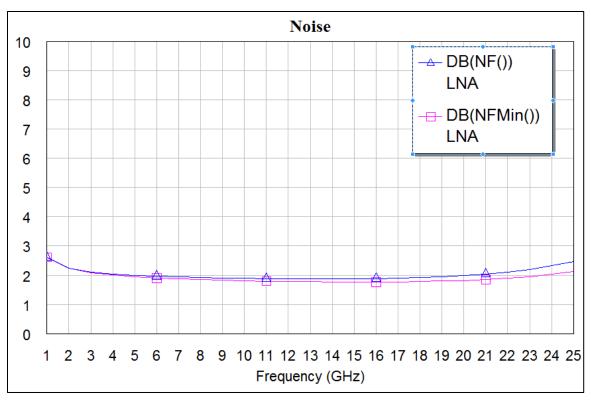

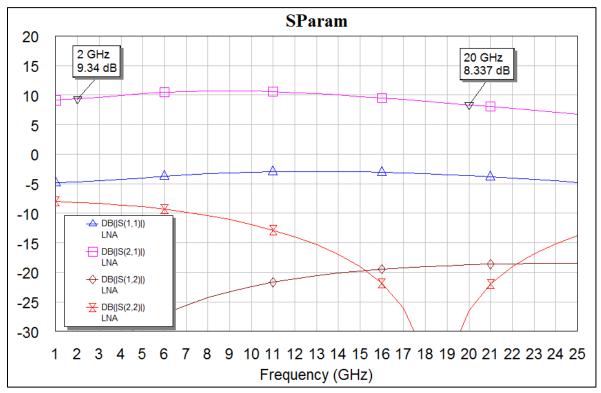

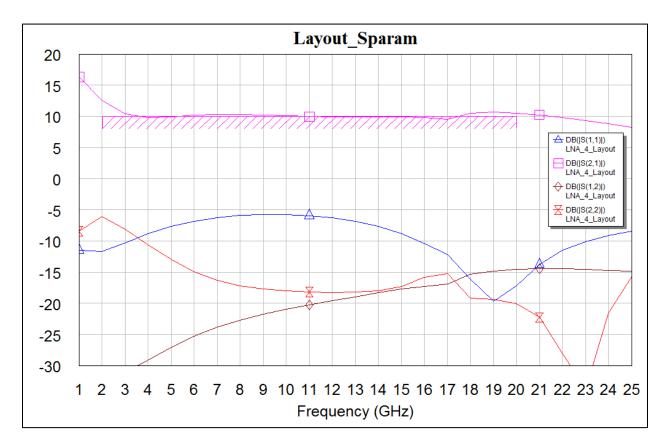

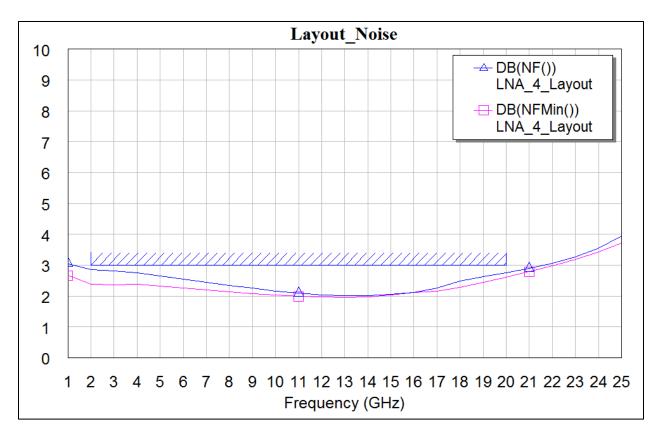

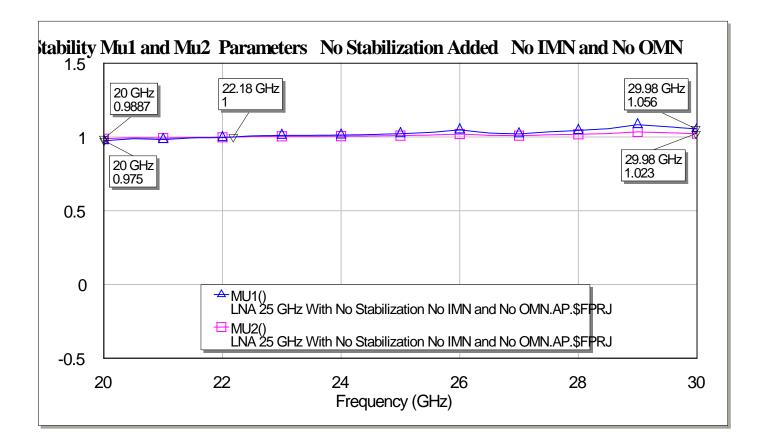

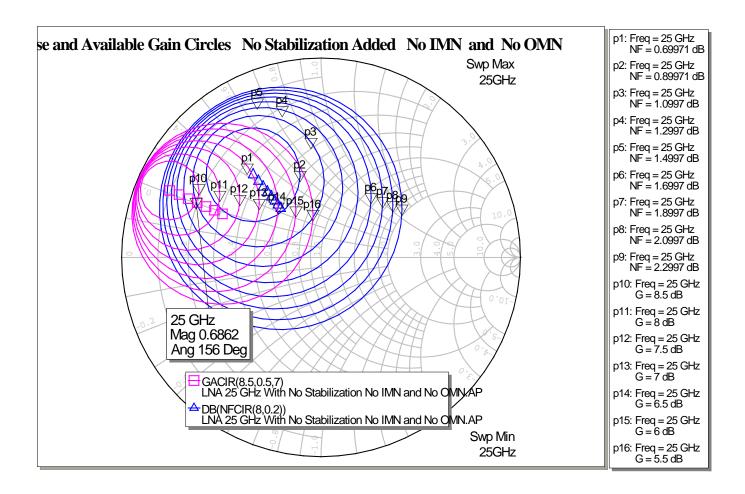

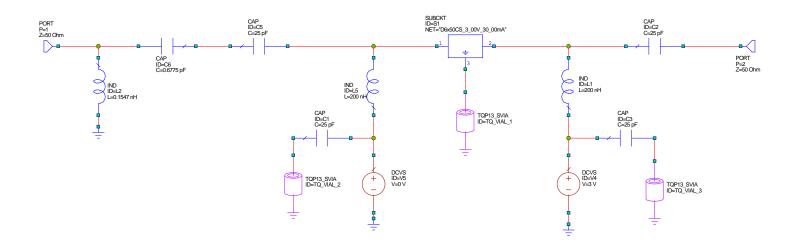

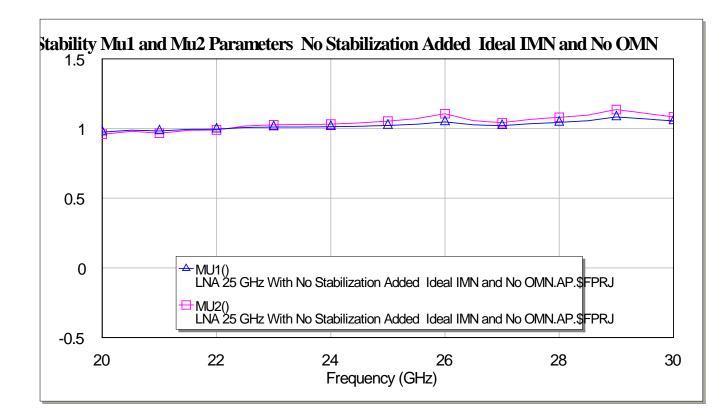

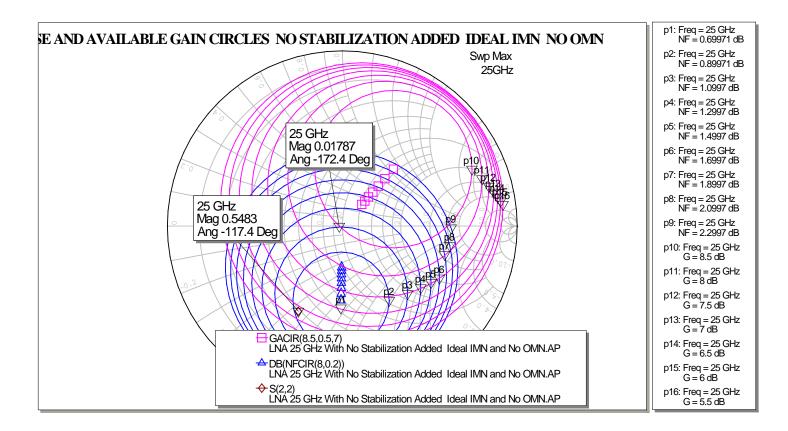

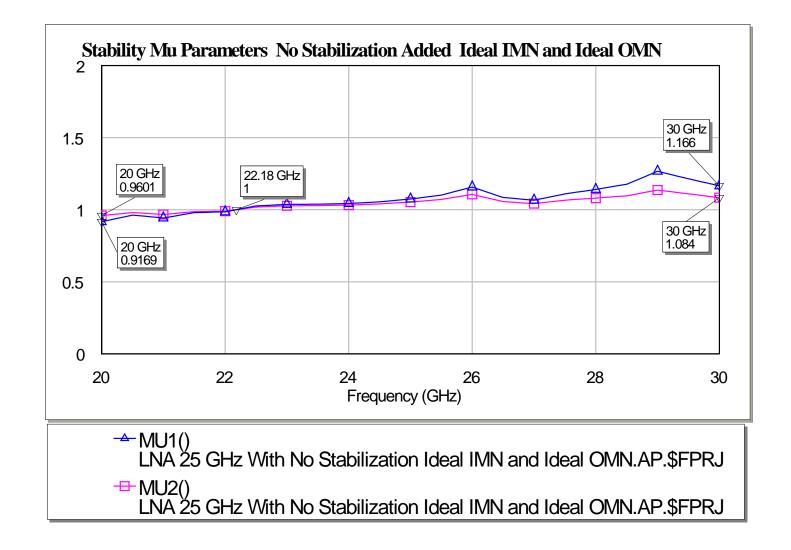

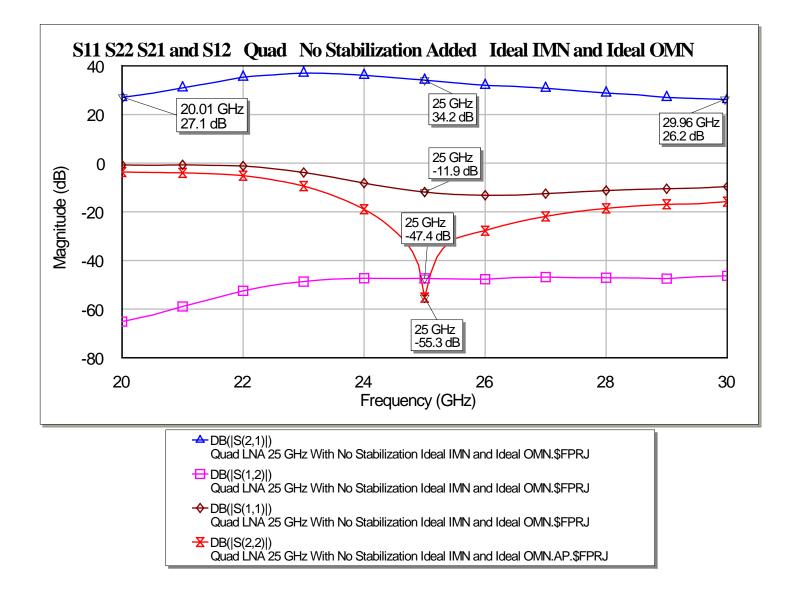

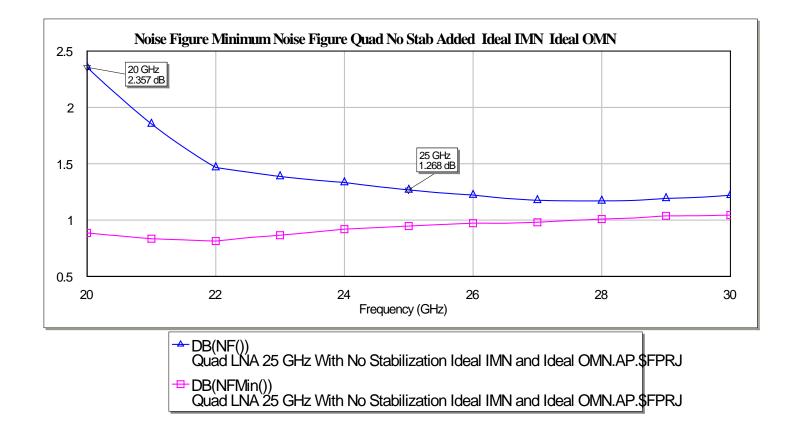

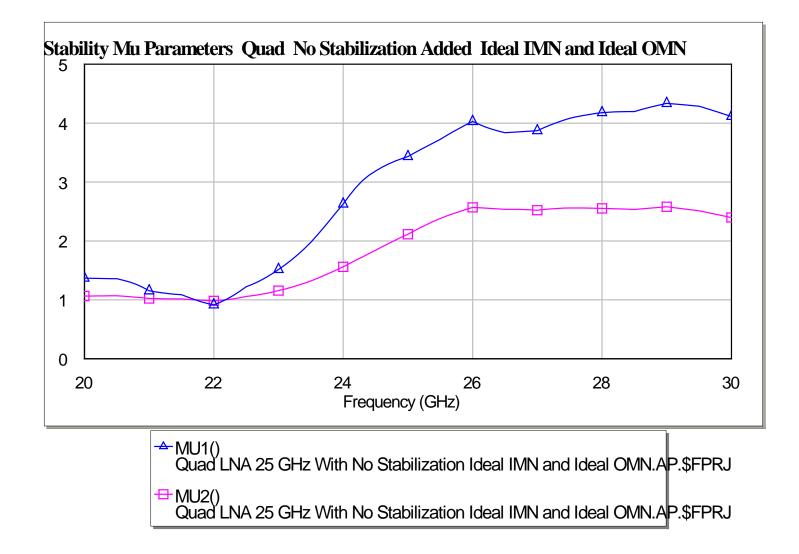

#### **ABSTRACT**