THE JOHNS HOPKINS UNIVERSITY G. W. C. WHITING SCHOOL of ENGINEERING ELECTRICAL ENGINEERING PROGRAM

MICROWAVE ENGINEERING

MMIC DESIGN 525, 787

**PROJECT REPORTS**

# -

# MMIC DOUBLE BALANCED MIXER E Adler and E Viveiros ACTIVE CIRCULATOR

G Polacek and R Meissner

MEDIUM POWER AMPLIFIER J Roussos and D Boulanger

2 db – 4 dB SWITCHED ATTENUATOR LJ Moskowitz and SR Turnquist

8 dB - 16 Db SWITCHED ATTENUATOR M Pacek and K Faison MMIC ELLIPTIC FILTERS Charles Cook

INSTRUCTORS: CRAIG MOORE AND JOHN PENN DECEMBER 20, 1989

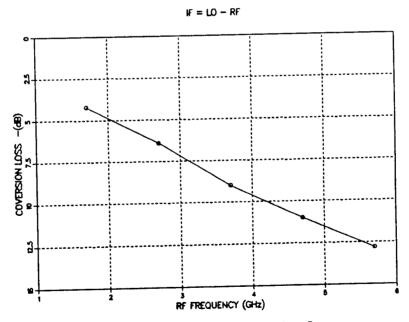

# MMIC DOUBLE BALANCED MIXER

# ERIC ADLER and ED VIVEIROS

DECEMBER 11,1989

# MMIC DESIGN 525.787 PROFESSORS CRAIG MOORE and JOHN PENN

### **Conclusions and Recommendations**

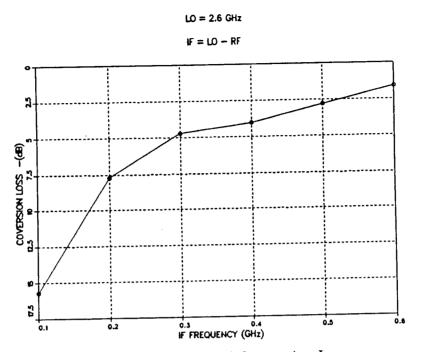

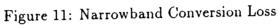

Computer simulations performed on the mixer, which included a FET ring and active baluns, revealed that the design met or exceeded all the required specifications. A maximum conversion loss 10 dB is achieved for RF and LO frequencies from 2 to 4 GHz with an IF from .2 to .6 GHz. The limitations in the IF bandwidth is mainly caused by roll off of the DC blocking capacitor. A larger value capacitor would extend the usable range closer to DC. The RF and LO baluns are more lossy at higher frequencies and the amplitude and phase matching also degrades as the frequency increases. This causes more loss in the mixer for higher RF and LO frequencies. The yield analysis indicated the mixer conversion loss would remain under 10 dBm over the process variation.

LO - RF isolation was observed to be -49 dB at an LO of 2.6 GHz. The actual isolation is expected to be worse due to coupling and parasitics in the circuit which could not be accounted for since the circuit layout could not be simulated. Compression simulations of the RF input didn't show the 1 dB compression point as the RF was swept from -60 to 0 dBm. The linear analysis of the RF, LO, and IF balun circuits indicate the RF compression point would be above the -20 dB goal. The actual compression point is expected to be lower than that shown in the linear analysis of the baluns since the ring FETs are only 48  $\mu$ m which is much smaller then the 150  $\mu$ m FETs used in the baluns. VSWR simulations were unattainable for the final mixer design due to the inability to characterize the ring FET for linear analysis. Return loss (VSWR) simulations performed on the RF/LO and IF baluns, which were modeled in a 50  $\Omega$  environment, are the only indications of the expected results. The return loss for the RF/LO balun was 11 dB min. and 8 dB min. for the IF balun.

The conversion loss could be improved by adding a bias to the ring FETs to select the desired operating condition. A circuit was simulated with the ring biased which showed a conversion gain of around 5 dB. This bias was not included in the final design due to space limitations. Circuit performance could have been improved if the input impedance of the ring FETs could have been determined. A better match between the ring and the balun circuits could then be achieved.

Figure 12: Wideband Conversion Loss

20

•

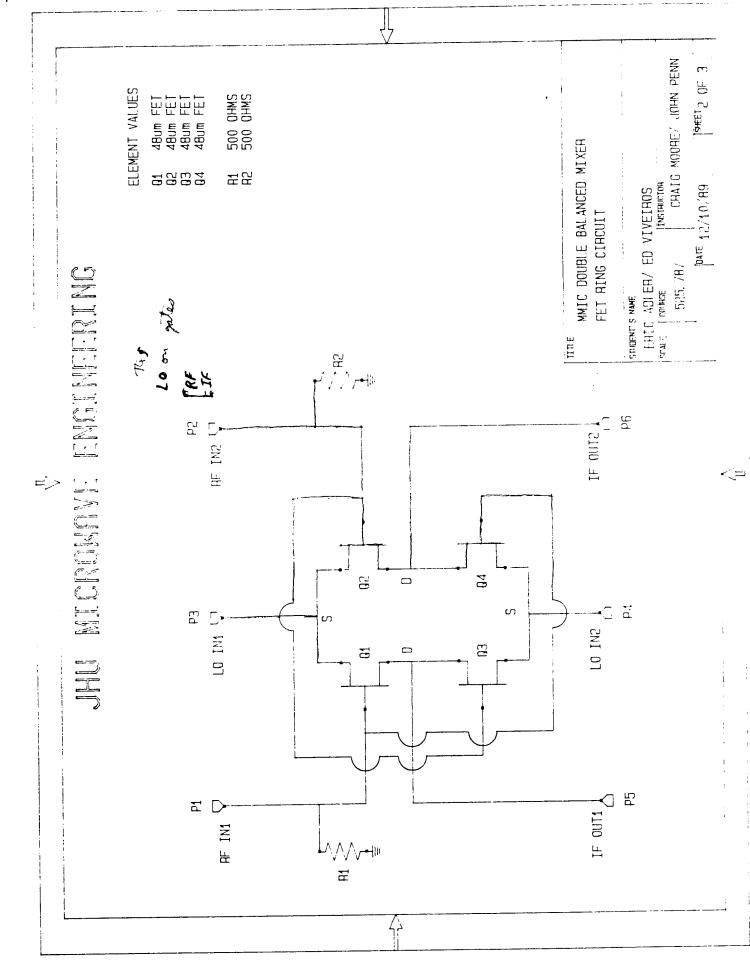

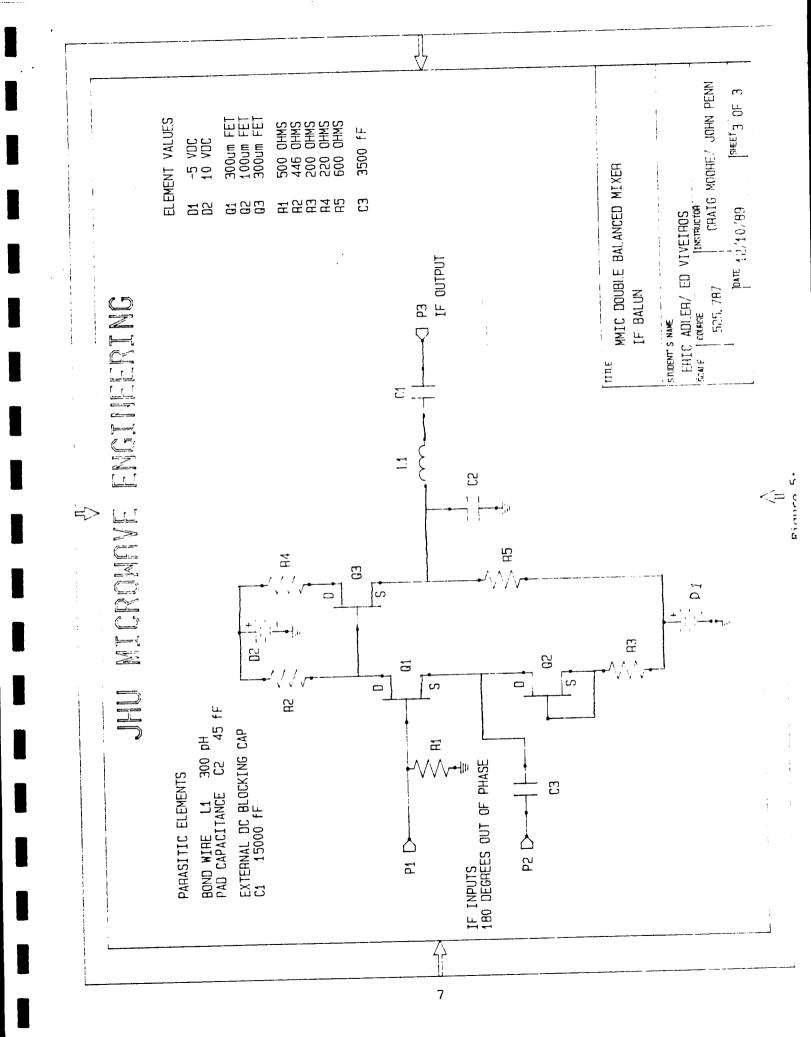

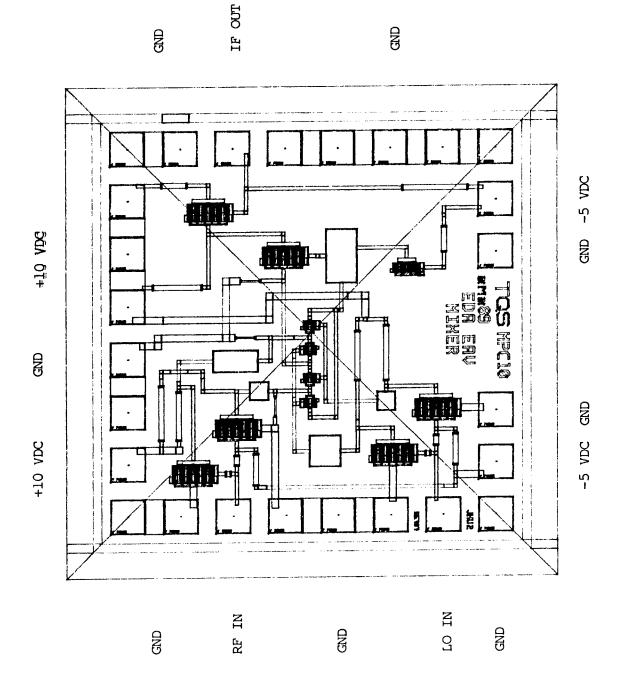

Figure 14: Final Circuit Layout

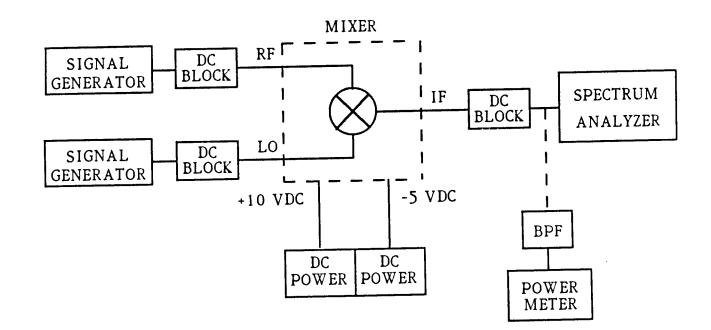

Equipment List:

2 Signal Generators - 1-6 GHz, -20 to 0 dBm

- 1 Spectrum Analyzer .1-6 GHz

- 2 DC Power Supplies -5 to +10 Volts

- 3 DC Blocking Capacitors 15 pF min.

- 1 Bandpass Filter (fixed or tunable) pass 100-600 MHz

- 1 Power Meter -40 to 0 dBm

Figure 17: Test Equipment Configuration

#### Active Circulator Final Report

i

. . . ·

Prepared for: 525.787 MMIC Design December 11, 1989

Submitted by: George Polacek and Robert Meissner

#### Specification Compliance Matrix

|                             | SPECIFICATION | GOAL       | MODELED PERFORMANCE <sup>1</sup> |

|-----------------------------|---------------|------------|----------------------------------|

| FREQUENCY                   | 2 - 6 GHZ     | 1 - 10 GHZ | 1 - 10 GHZ                       |

| ISOLATION                   | 10 dB min.    | 16 dB      | 18 dB                            |

| INSERTION LOSS              | $5 dB^2$      | 1 dB       | 4 dB                             |

| VSWR                        | 2.5:1 max.    | 1.5:1      | 1.35:1                           |

| POWER @ 1 dB<br>COMPRESSION |               | +10 dBm    | +12 dBm                          |

<sup>1</sup> - The limits of the operating frequency are taken to be the points where modeled performance fails to achieve any of the specifications. All of the other modeled performances listed are the worst case performance over the frequency range 2 to 6 GHz.

$^2$  - There was no specified limit on the insertion loss, but we have accepted the 5 dB goal that the author in reference 1 chose for insertion loss.

#### 7. CONCLUSIONS AND RECOMMENDATIONS

#### <u>Conclusions</u>

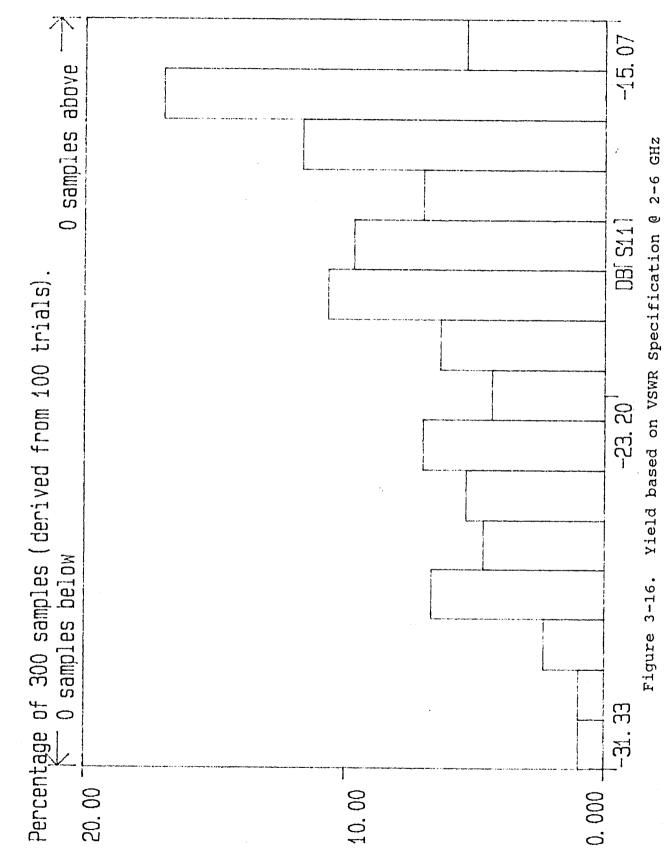

The proposed circulator meets all of the specified performance measurements and even exceed most of the goals. The yield analysis predicts that 93% of the units produced will meet the requirements.

Therefore, because most of the known parasitics have been included in the modeling and because the predicted performance greatly exceeds the specifications; there is high confidence that the chip when it is actually tested will achieve the specifications from 2 to 6 GHz.

Furthermore, should the circulator achieve the predicted 1 to 10 GHz bandwidth, this design would be a marked improvement over the design in Reference 1.

#### Recommendations

The design of a MMIC chip is an iterative process and while we are pleased with the predicted results, we are not satisfied. Given more time, there are several areas in which further analysis/relayout could yield improved performance.

- 1. Convert as much of the MLINs as possible to Metal 2. This should reduce the losses in the circuit.

- 2. Because of physical constraints, each leg of the circulator are not identical. More could be done to improve this.

- 3. Because performance improved with the addition of the bond wires, perhaps series inductance could be added to the input of each port.

- 4. The common source greatly affects overall performance and thus a final look at optimizing the component values may improve the results.

#### REFERENCES

1. Dougherty; Microwaves & RF Magazine; June 1989; pp 85-89

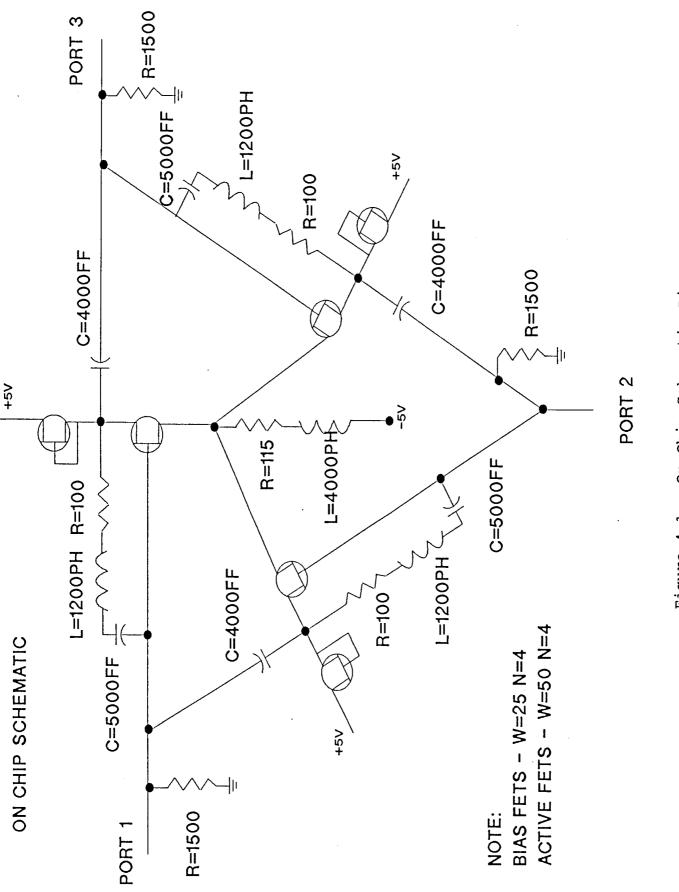

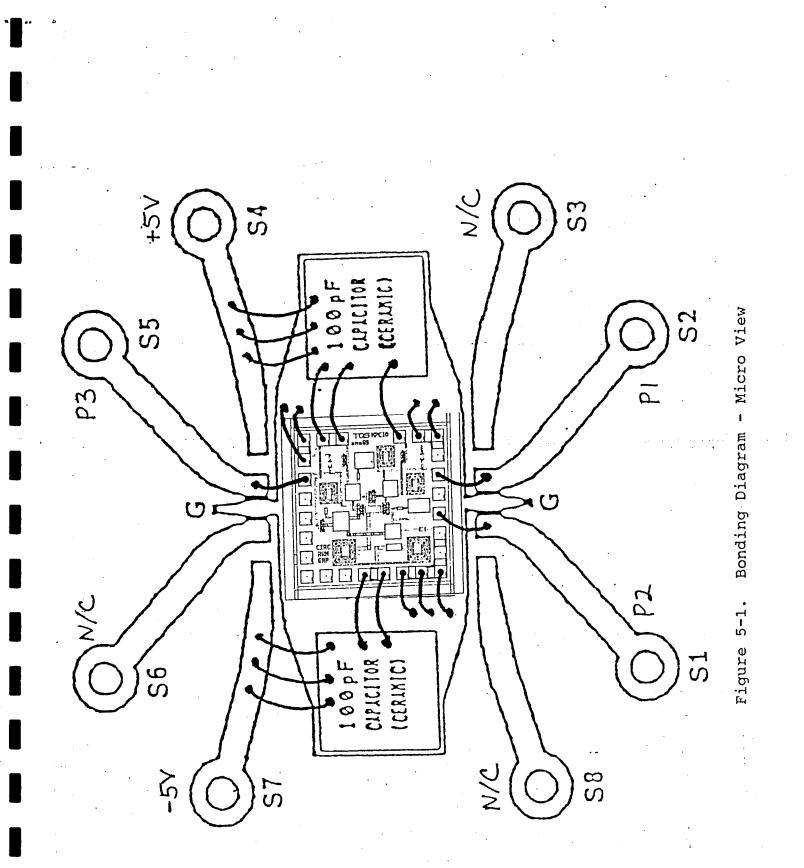

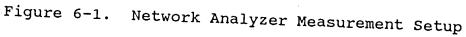

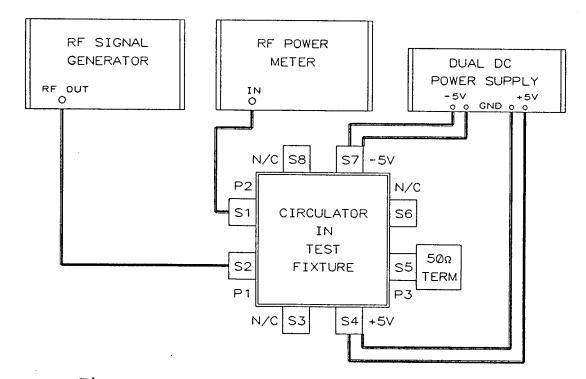

On Chip Schematic Diagram Figure 4-1.

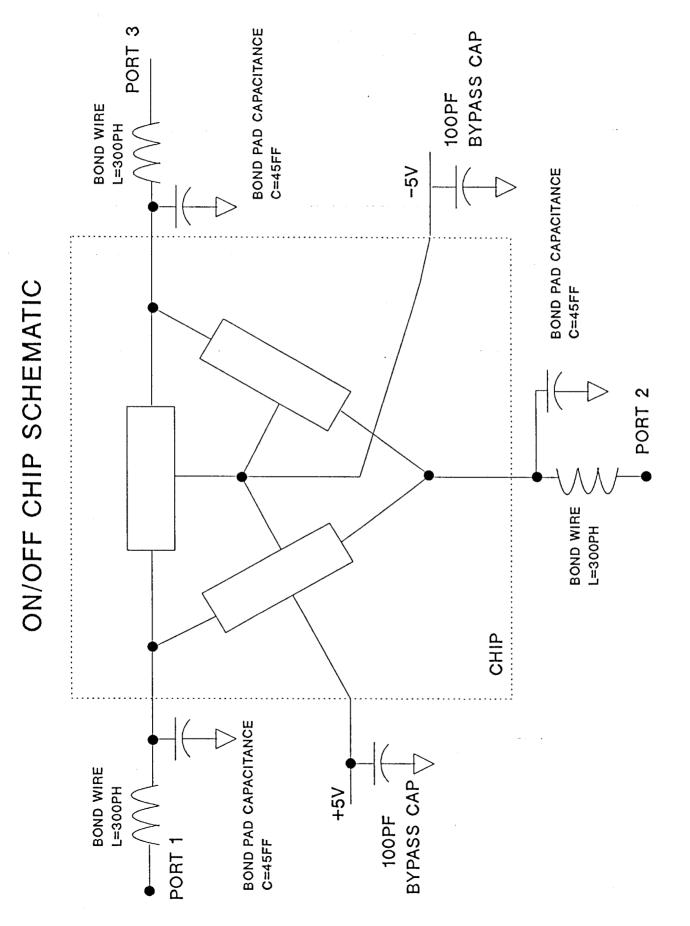

Figure 4-2. On and Off Chip Schematic Diagram

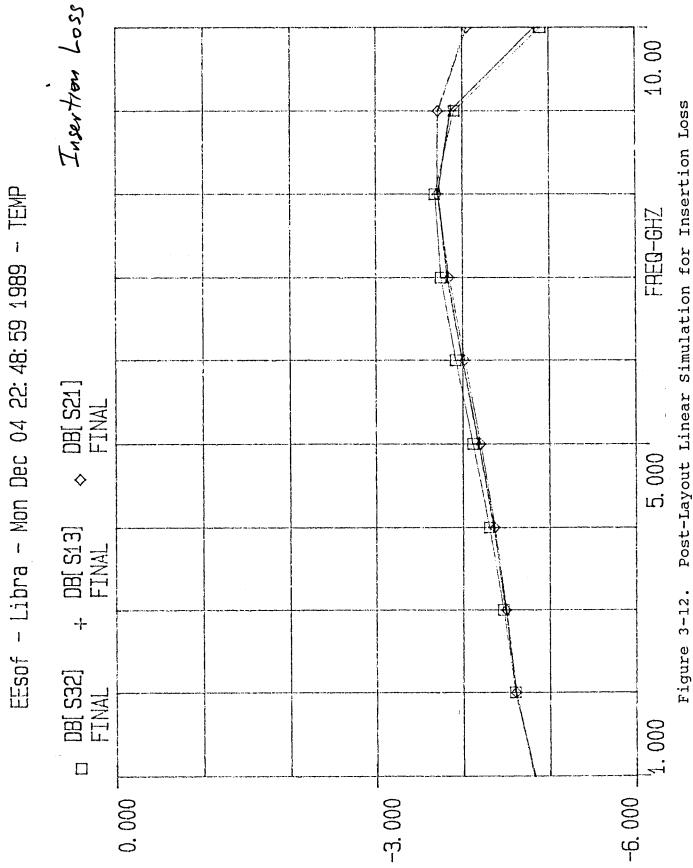

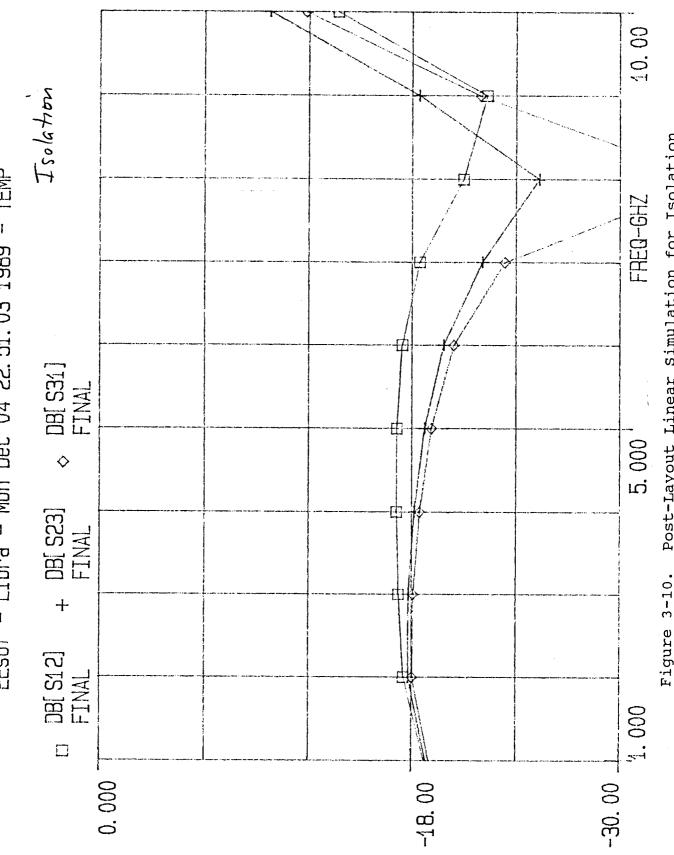

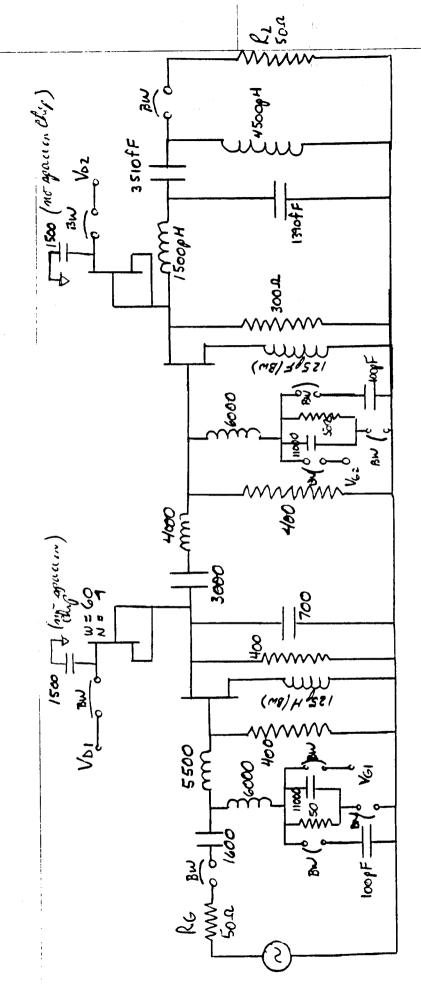

EEsof - Libra - Mon Dec 04 22:51:03 1989 - TEMP

Post-Layout Linear Simulation for Isolation

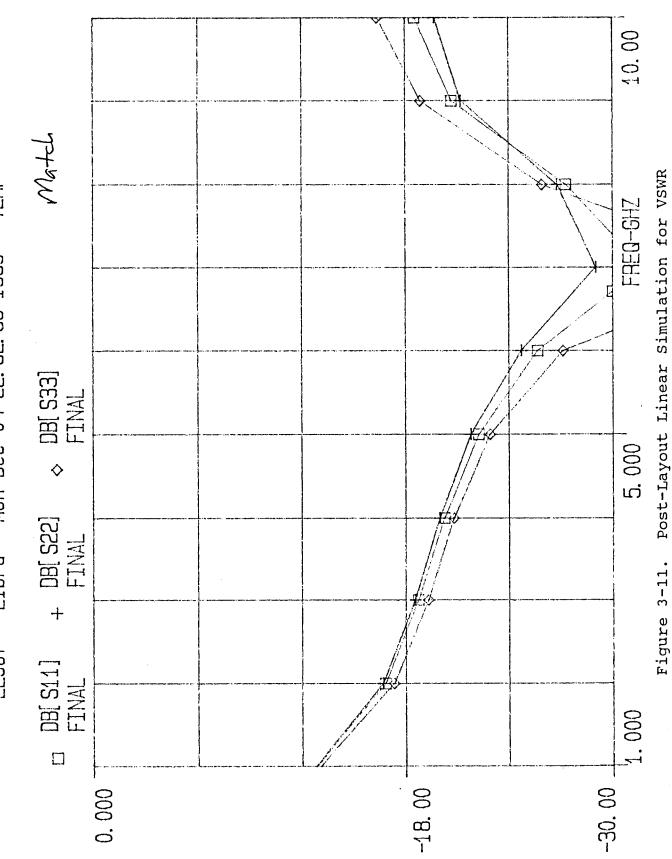

EEsof - Libra - Mon Dec 04 22:52:56 1989 - TEMP

Post-Layout Linear Simulation for VSWR

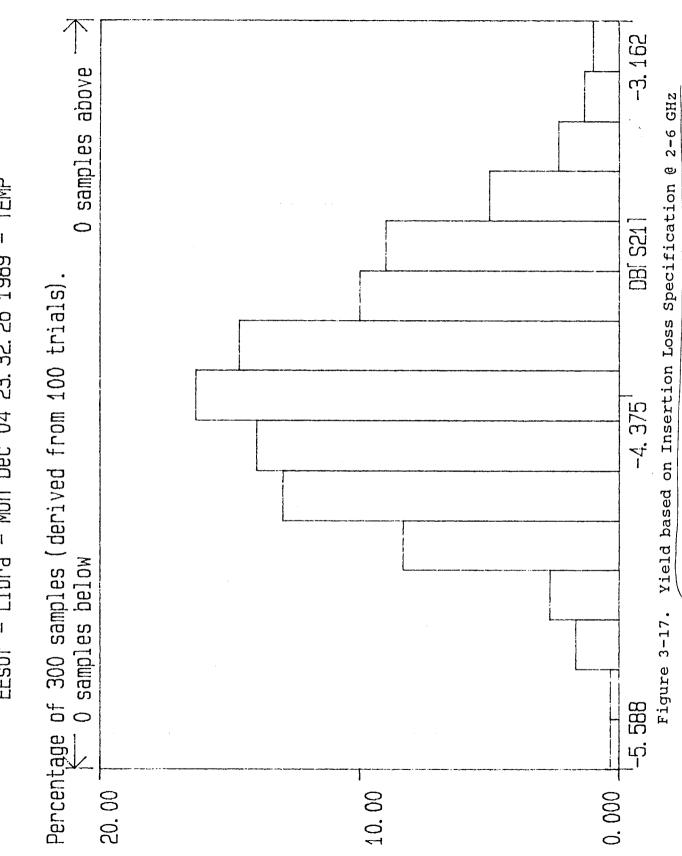

EEsof - Libra - Mon Dec 04 23: 32: 26 1989 - TEMP

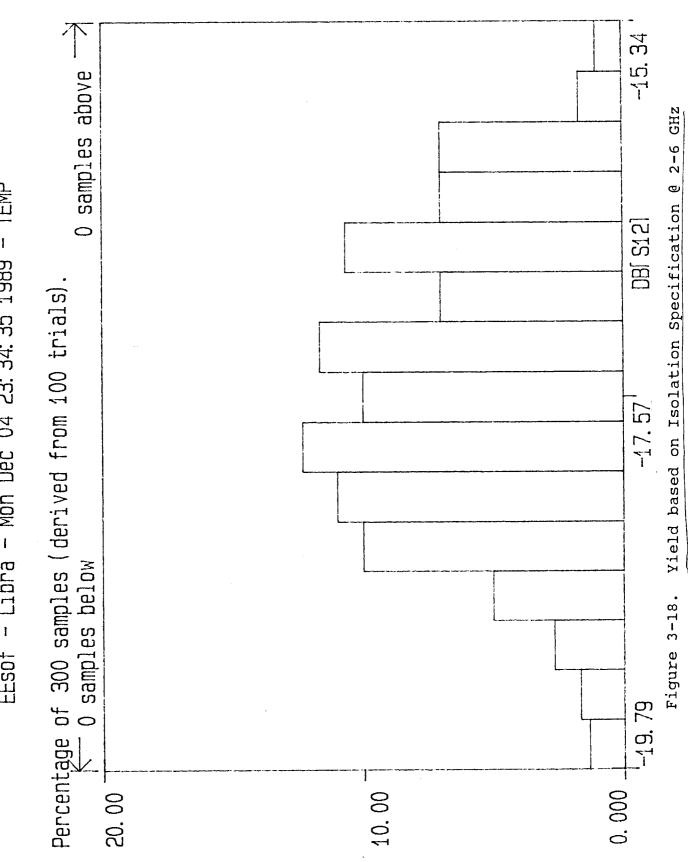

EEsof - Libra - Mon Dec 04 23: 34: 35 1989 - TEMP

EEsof - Libra - Mon Dec 04 23: 30: 27 1989 - TEMP

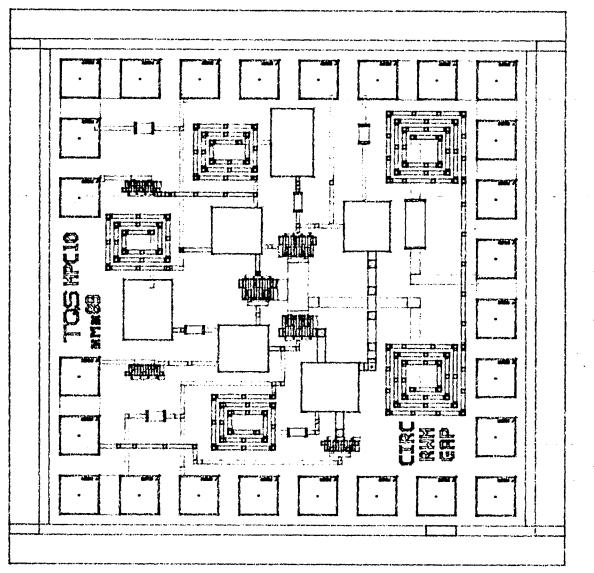

Active Circulator Layout Figure 5-3.

**→** • • • • •

:

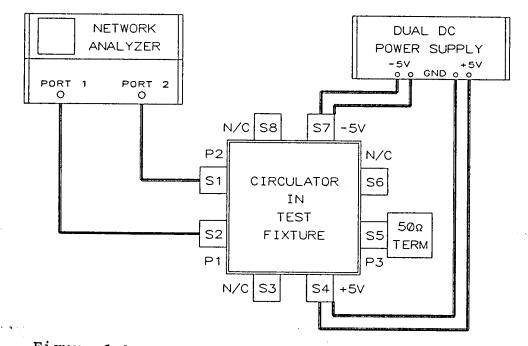

Figure 6-2. Power Meter Measurement Setup

Dec 11th, 1989

# MMIC DESIGN 525.787

.

FINAL PROJECT : MEDIUM POUDE AMPLIFICK

By & JASON ROUSSOS DENIS BOULANED

### INTRODUCTION

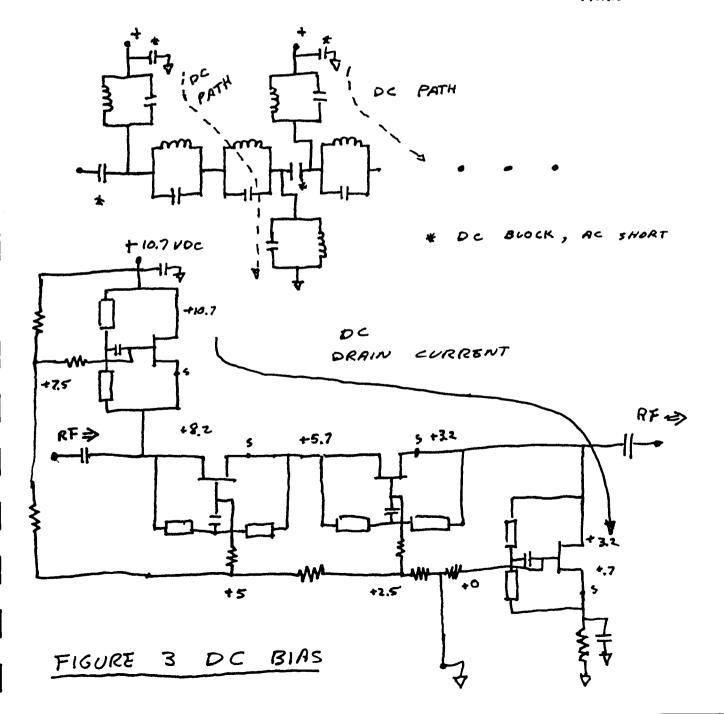

CIRCUIT DESCRIPTION : the medium power anglifier is a tur-Stope anglific using a 300 m FET at the ment and a 1200 m FET lit the outquit. The matching circuits are the involut, interstage and the output. Active bias are used for each FET to sure t the meternal inductor which will block the core of the package to fit property. FET 2 FETI HA-HHSM HA-HUSTI W = 50mN = 6 $W = 100 \mu$ Figure 2.1 MPA RF schemalic. the input matching circuit is design to provide good situan loss over the band of interest and subtore matiching to dicing the interstorge matching circuit is duisn to achieve the Harget gain with an excellent flat new over the band. The out put matching circuit is design to provide the segurici Pide and reasonable return lose. The bias point are selected to provide the output power with reasonnable efficiency. But the use of active bias is degraching the efficiency by 33%.

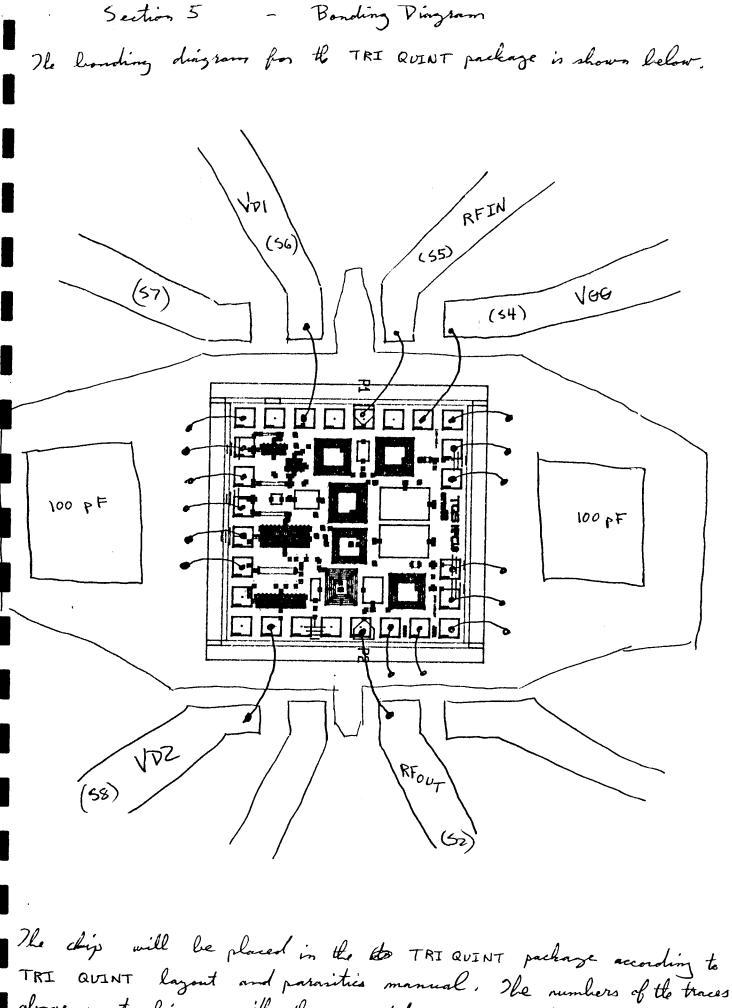

Section 4 - Schematic Diagrams

A schematic diagrams is included in the main report for the pre lagour arient. Note the inclusions of bondwise parasities. A schematic of the post layout circuit is not shown, but the layout and recersar connections (and parasities resulting from these connections) is shown below (11) n/ INK IIK SPH 11 神 **ノ**川 叭 111 IN 111 )))/11 Hel 202 =-RF in

Paravitic Note that "liandpad capacitances were not includeded in the nimilations due to their minimum effect at 2.5 GHZ (as determined in the LNA designs in HW # 5), Each homeluise was assumed to have 300 pH inductance (300 pm length).

4. SHEMATIC DIABRAMS

## 3. - SPECIFICATION COMPLIANCE MATRIX

·

| PARAMETER        | SPECIFICATION | SIMULATED RESULTS                           |

|------------------|---------------|---------------------------------------------|

| FREQUENCY        | 2-3 GHZ       | 1.8-3.2 642                                 |

| GAIN             | 15 JB Min     | 18.5 dismin                                 |

| GAIN RIPFLE      | +/- 1dB       | ±.25 d3                                     |

| Pidis            | +20 dibm muis | +19dBmi<br>? (uning Kangthien mole),        |

| I/P 12/2         | 7.5 dis       | >12.5 d.3                                   |

| 0/7 R/L          | 7.5 di2       | 76.C dis                                    |

| n(%)<br>at P.1.3 |               | 4. 8 To ACTIVE BIAS<br>14.7 The ACTIVE ISAS |

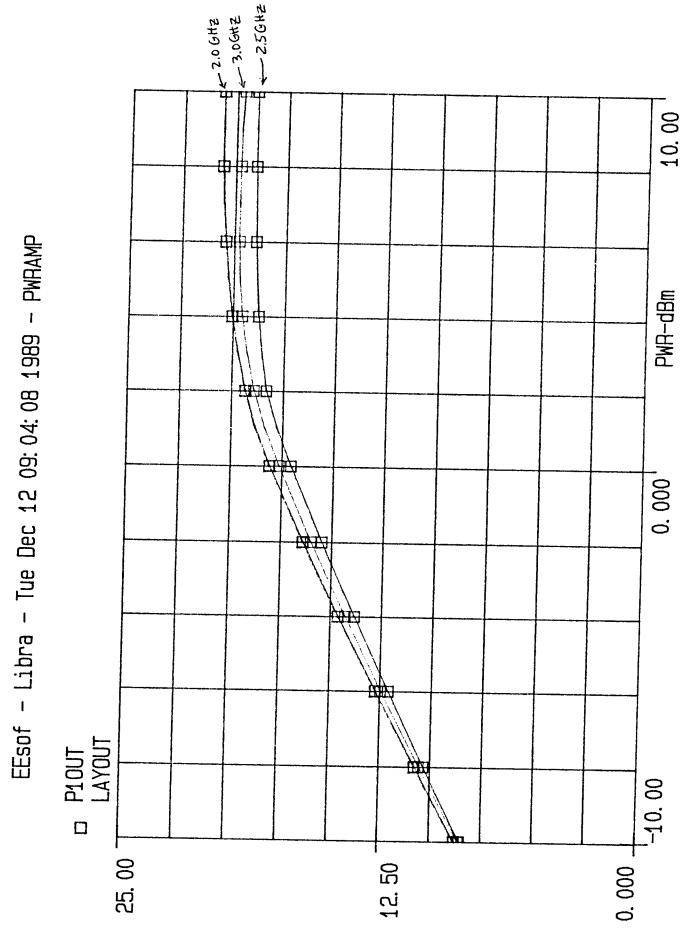

EEsof – Libra – Tue Dec 12 08: 47: 39 1989 – PWRAMP

above must line up with the appropriate SAIA connectors on the package.

#### MMIC DESIGN COURSE

#### FINAL PROJECT

THE 2db AND 4db STAGES OF A SWITCHED ATTENUATOR

Project Engineers:

Larry J. Moskowitz 9215 Marydell Rd. Ellicott City, Md. Phone: Hm: 750-3963

,

1. . .

ſ

Wk: 765-3178

Scott R. Turnquist 637 Chase Ave. Annapolis, Md. Phone: Hm: 267-9478 Wk: 266-4720

-

December 11, 1989

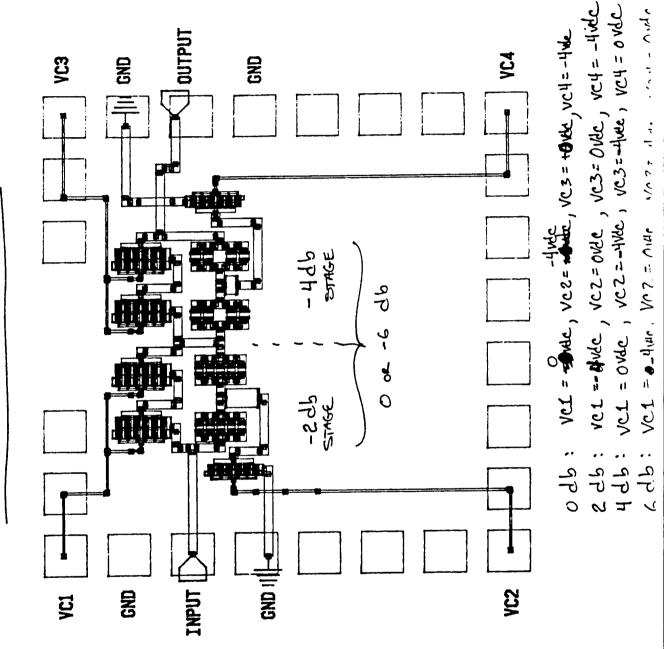

#### Section 2: INTRODUCTION

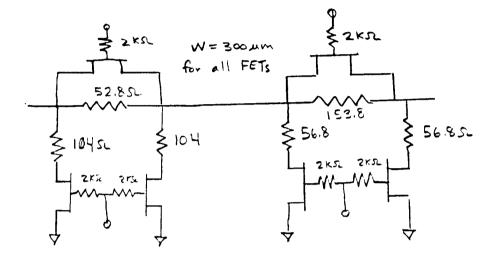

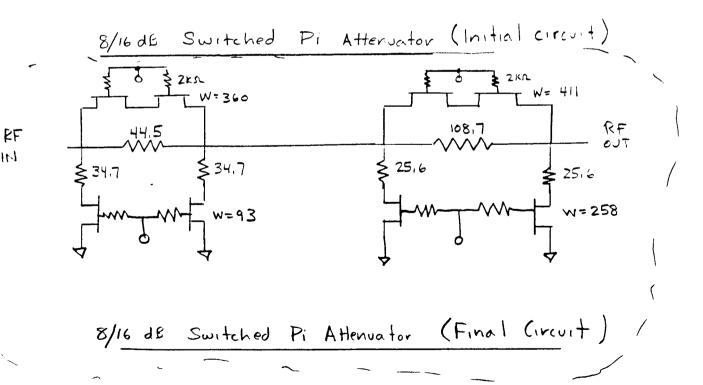

The goal of this project was to develop and simulate a switched four stage attenuator. The attenuator stage value requirements were 2, 4, 8, and 16 db which originally were to be cascaded together for varying levels of attenuation between 0db and 30 db. Two teams of two people were working this problem. There were 8 leads available for input and output to the attenuator because of the mounting structure used for the final chip. Because of this, the 2/4 db stages and 8/16d db stages were not cascaded and share voltage control signals. The following write-up details the efforts of the team responsible for the 2db and 4db stages of this attenuator.

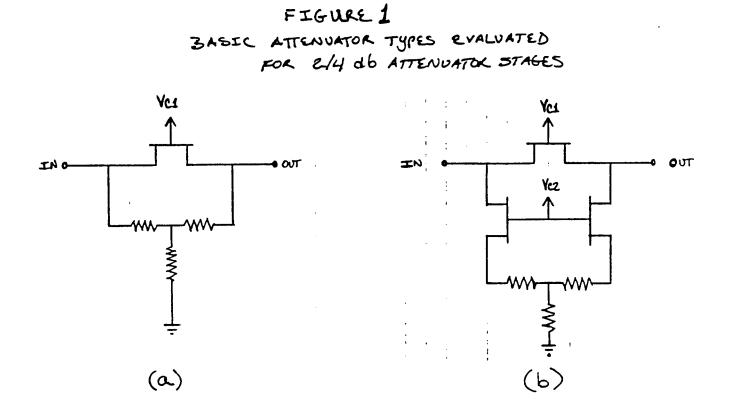

Sections 3 and 4: Modeled Performance and Schematic Diagrams

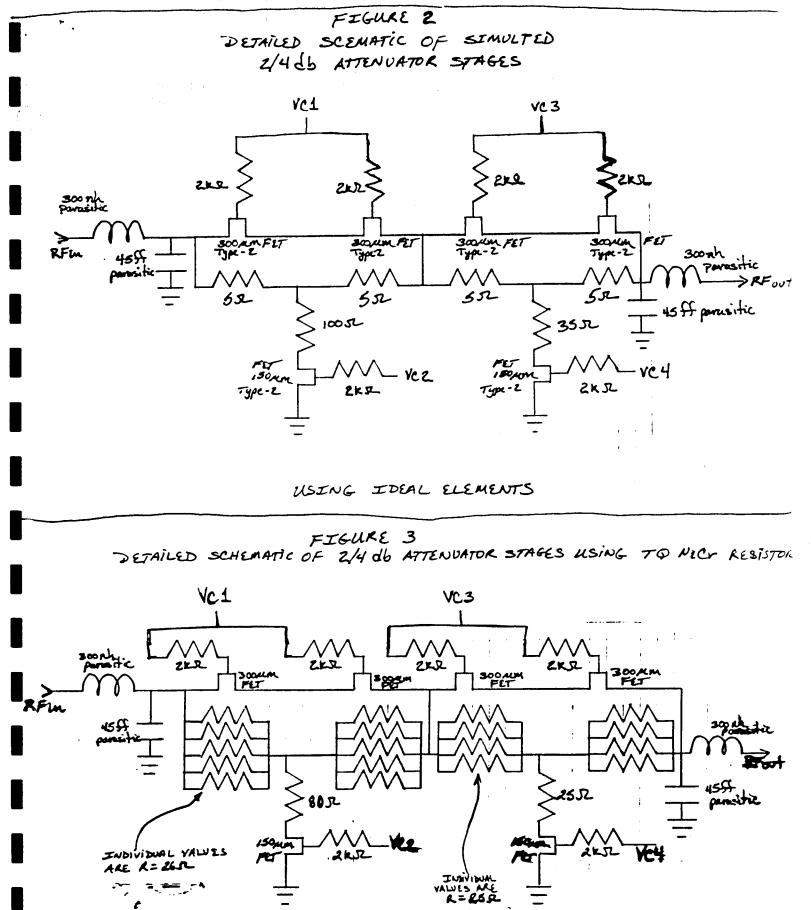

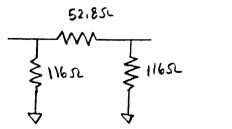

Several possible circuit designs were developed and simulated for this project. Figure 1 provides the three basic circuit types which were simulated and varied in order to achieve the design used in this project. Ultimately Figure 1c was the best performer; Figure 2 provides a detailed circuit diagram of the ideal elements used to form the attenuator stages. The same FETs were used in both stages and only the pad resistors needed to be varied to provide the needed attenuation levels. Figure 3 provides the circuit schematic representing the same circuit using Triquint NiCr resistors. Since the minimum value for these resistors was 25 Ohms, several resistors had to be placed in parallel to form the proper resistive values for each pad.

In all simulations except the intermodulation performance analysis, a linear model made up of scaled ideal lumped components was used to provide the characteristics of the 300 and 150 micron FETs used in these circuits. This was done since the FETs are being used as switches with the input on the drain and the output on the source. For both FETs two linear models were used. One model represents the FET characteristics when it is on and the other is used for the off condition. Figure 4 provides the schematic diagram of the linear FET model used in these analyses as well as the baseline values which are scaled in order to model the 150 micron FET.

To assess the 3rd order intermodulation intercept point of the circuit The Raytheon-Statz model of each FET was used and only the 0 db attenuator configuration was evaluated. This is because it is assumed that the characteristics of the attenuator stage bypass FETs will drive the worst-case intermodulation intercept.

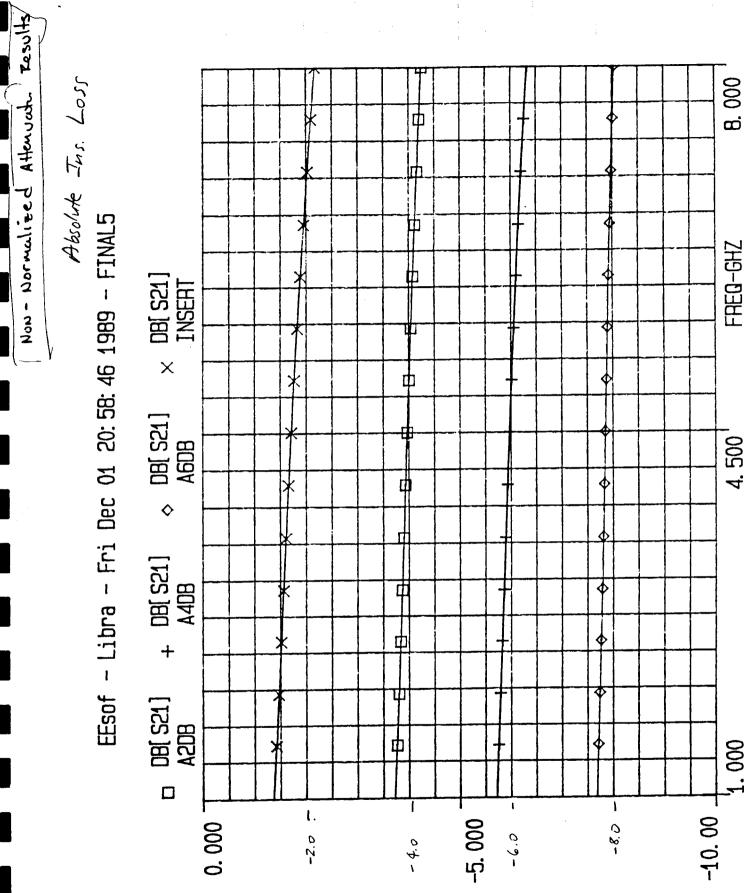

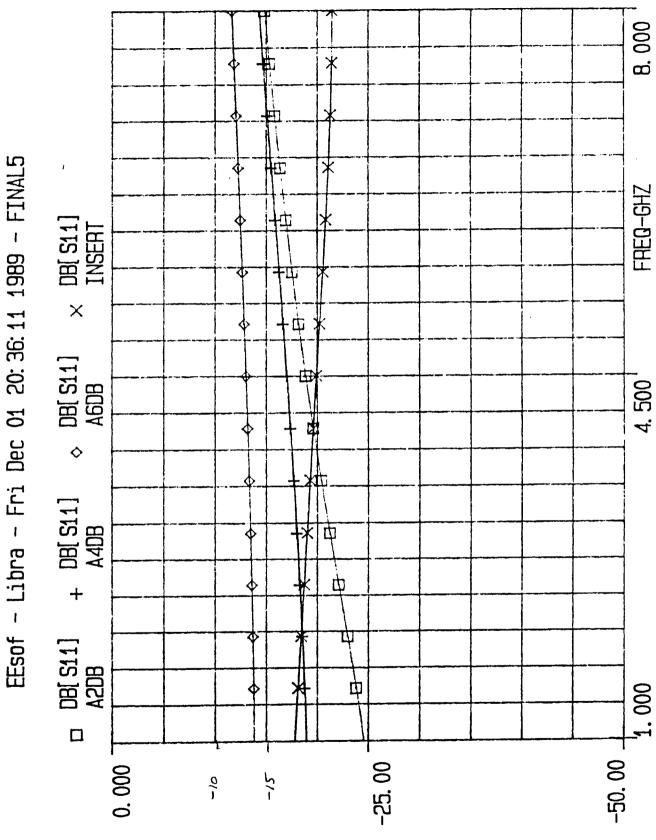

Table 1 provides a summary of the various pertinent design simulation results. Table 2 provides the yield analysis results of the final circuit simulation.

USING TRIQUINT NICT RESISTORS

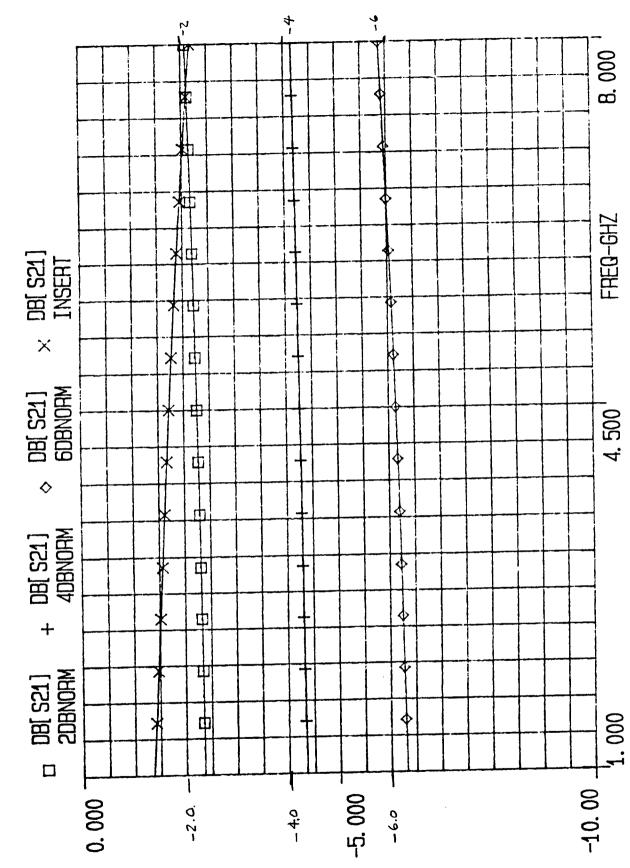

Affenvetor Values Normalized to Insertion Loss Using process Black

÷

Relative Ins. Loss EEsof – Libra – Fri Dec 01 20:19:32 1989 – FINAL5

EEsof - Libra - Fri Dec 01 20: 42: 09 1989 - FINAL5

- CIRCUIT SIMULATED IN LAOUT

1

,

8 AND 16 DB SWITCHED ATTENNATOR

MARK PACEK

KEVIN FRISON

12/11/59

\_<u>\_</u>\_\_\_\_

,

. . . . .

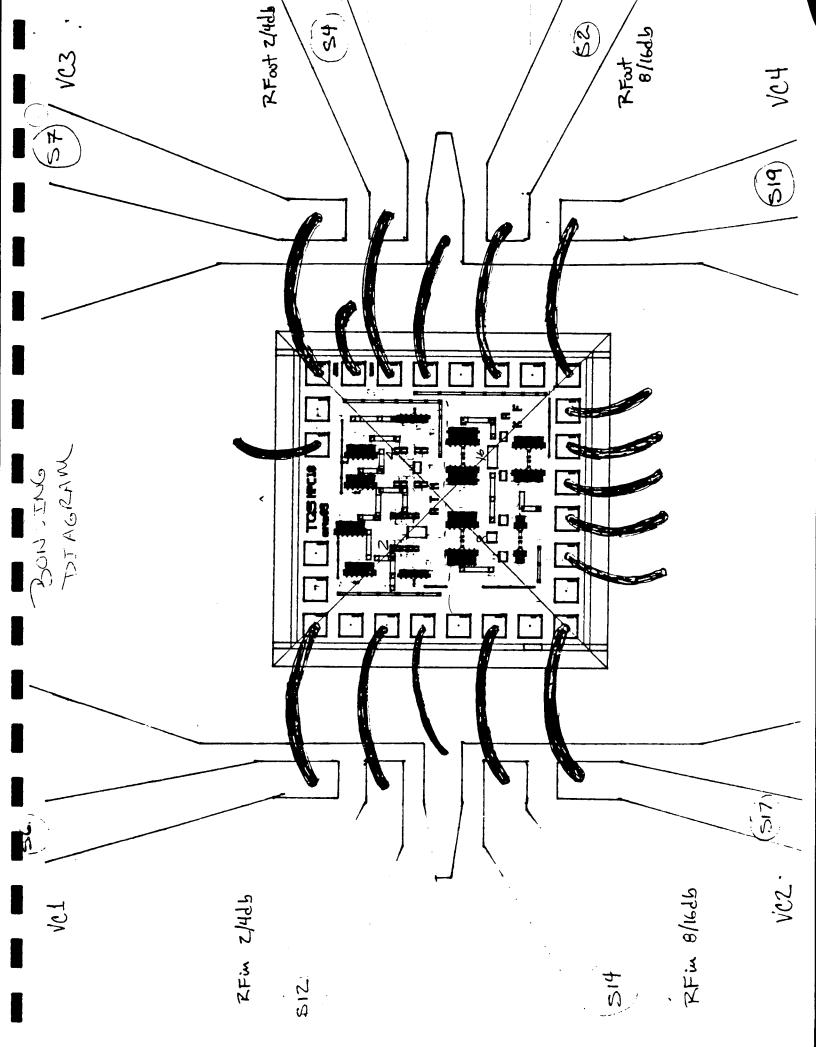

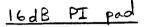

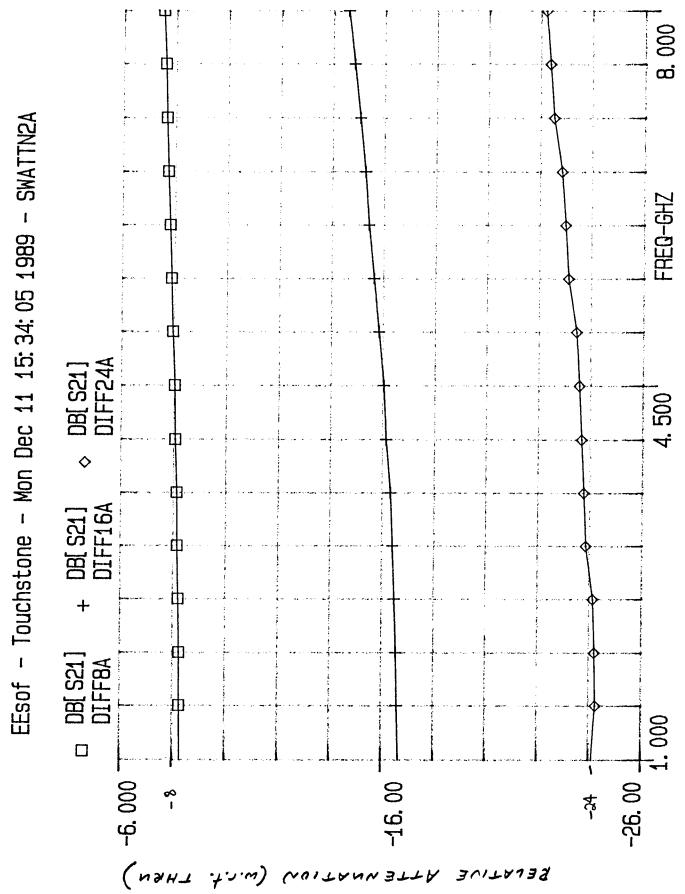

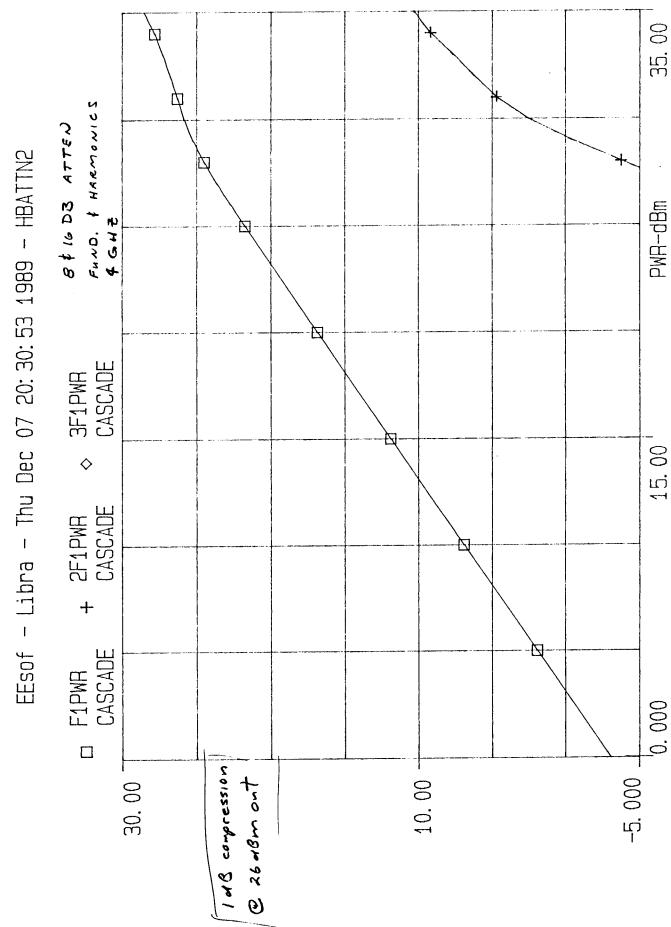

## Circuit Description

1

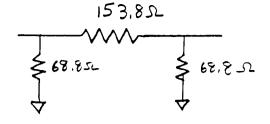

The 8 and 16 dB attenuator circuit is made up of two switched resistive PI networks connected in series (figure 1). Each attenuator section requires two control voltages. The thru path (no attenuation) is selected by turning the series FETs on (V+=0V) and the shunt FETs off (V-=-4V). The PI's are switched in when the shunt FETs are on (V1-=0V) and the series FETs are off (V1+=-4V). The shunt resistors have been adjusted to account for the drain to source resistance of shunt FETs. FET widths were selected on the basis of the output the intercept point requirement (OP3) and then optimized for RF performance. The circuit was designed using the latest in CAD software including TOUCHSTN for linear analysis, LIBRA for non-linear harmonic balance analysis and PSPICE for initial ouput compression point estimates. The circuit meets all performance goals, consumes minimal chip area and is process tolerant.

# Design Philosophy and trade-offs

The PI topology was one of three considered for the MMIC attenuator design. The others were the switched TEE and the switched path attenuators. The switched TEE network (figure 2) is the dual to the switched PI. It has a slight advantage in requiring one less resistor. It's main disadvantage for this application is the small size of the shunt resistor since the shunt FET resistance becomes the dominant resistance in the branch. Because Rds of the TQFET has a 3 sigma process variation of 14% vs. 3% for a NICR resistor, the accuracy of the TEE attenuator (for the 8 and 16dB case) is less process tolerant than the PI attenuator.

The switched path attenuator (figure 3) is made up of two back to back SPDT switches and a resistive pad. The two RF paths are identical with the exception of the the resistive TEE which is used to give the desired attenuation step. The number of FETs in the thru and attenuation path are the same. Since any variation in the FET switch parameters will be seen by both paths the attenuation step accuracy will be mostly dependent on control of the NICR resistors. Thus this circuit is excellent in terms of being process tolerant. This symetry also offers advantages in phase response. This attenuator showed very little phase shift between attenuation states whereas the PI attenuator had 40 degrees of shift between the 0 dB and 24 dB attenuation states at 8 GHz. Disadvantages between the switched path attenuator and the PI attenuator include increased complexity and area (16 FETS total vs. 8 for the PI), higher insertion loss, and a slightly lower output intercept point (OP3). This circuit could not be made to fit on the chip.

## Process Sensitivity

The prime contributor to variation in attenuation accuracy in the switched PI attenuator is variation in the on resistance of the FETs. Simulations were performed in which the FET gate widths were allowed to vary +/-10 percent. The worst case variation from the simulation with nominal components was found to be +/- 0.4 dB.

8de PI pad

1

١

1-11

Figure 1

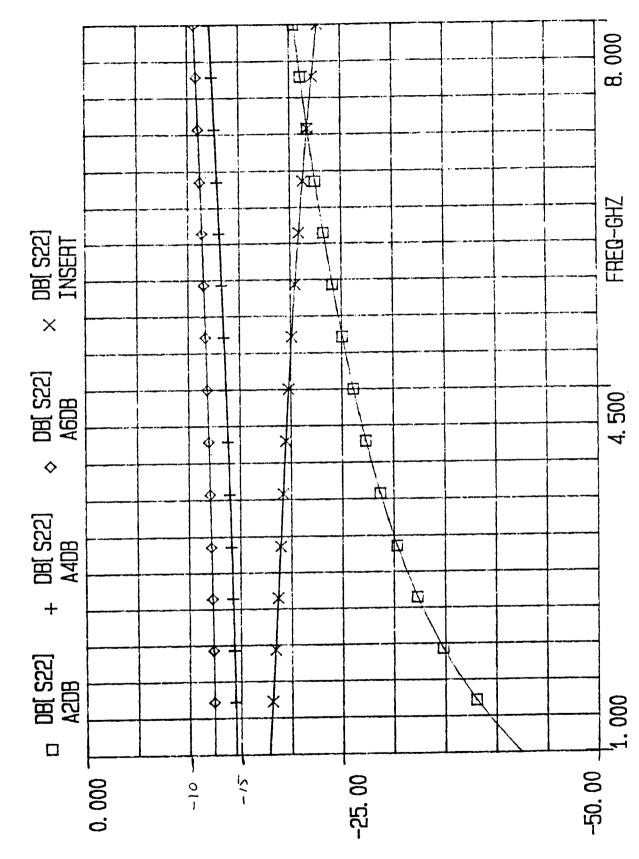

|                                                   |                                               |           |        |                | 8. 000                         |

|---------------------------------------------------|-----------------------------------------------|-----------|--------|----------------|--------------------------------|

| Be~ シノン G 2 4 C C C C C C C C C C C C C C C C C C | × DB[ S21]<br>24DBA                           |           |        |                | FREQ-GHZ                       |

| o. 6                                              | <ul> <li>◆ DB[ S21]</li> <li>160BA</li> </ul> |           |        |                | <b>4.</b> 500 <sup>1</sup>     |

| Lavour incen<br>Touchstone - Mor                  | + DB[ S21]<br>08DBA                           |           |        |                |                                |

| EESOF - T                                         | DB[ S21]<br>THRUA                             | 00 4 1    | 88     | - 7 <i>1</i> - | <br>-24 -<br>3. 00             |

|                                                   | ć                                             | (8a)<br>4 | CONTRA |                | <br>, <sup>24</sup><br>-28. 00 |

.

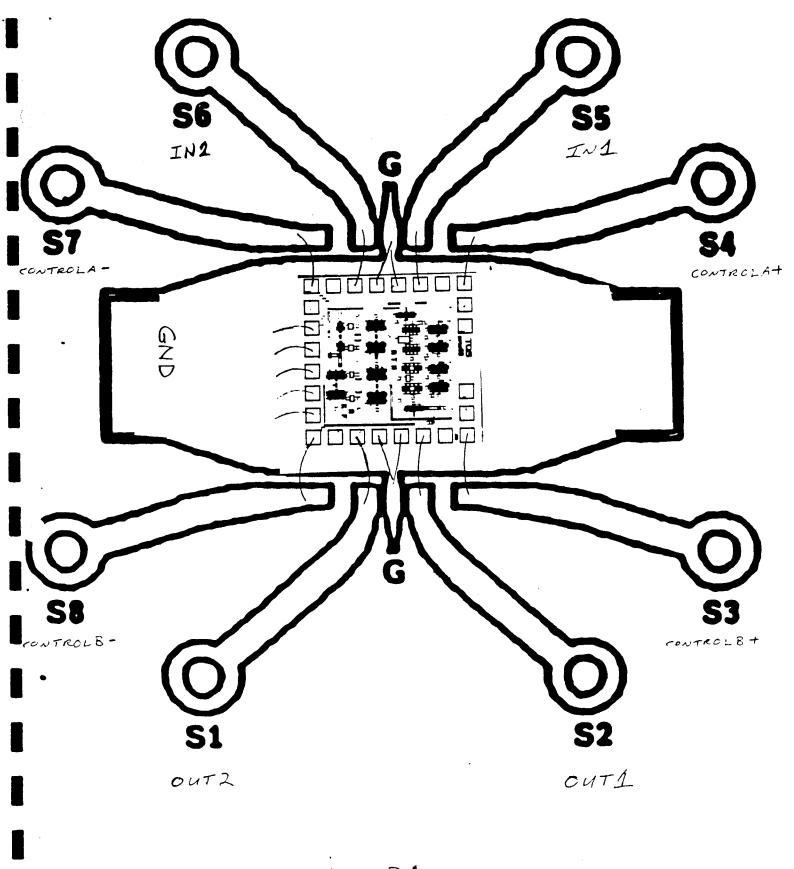

Figure.

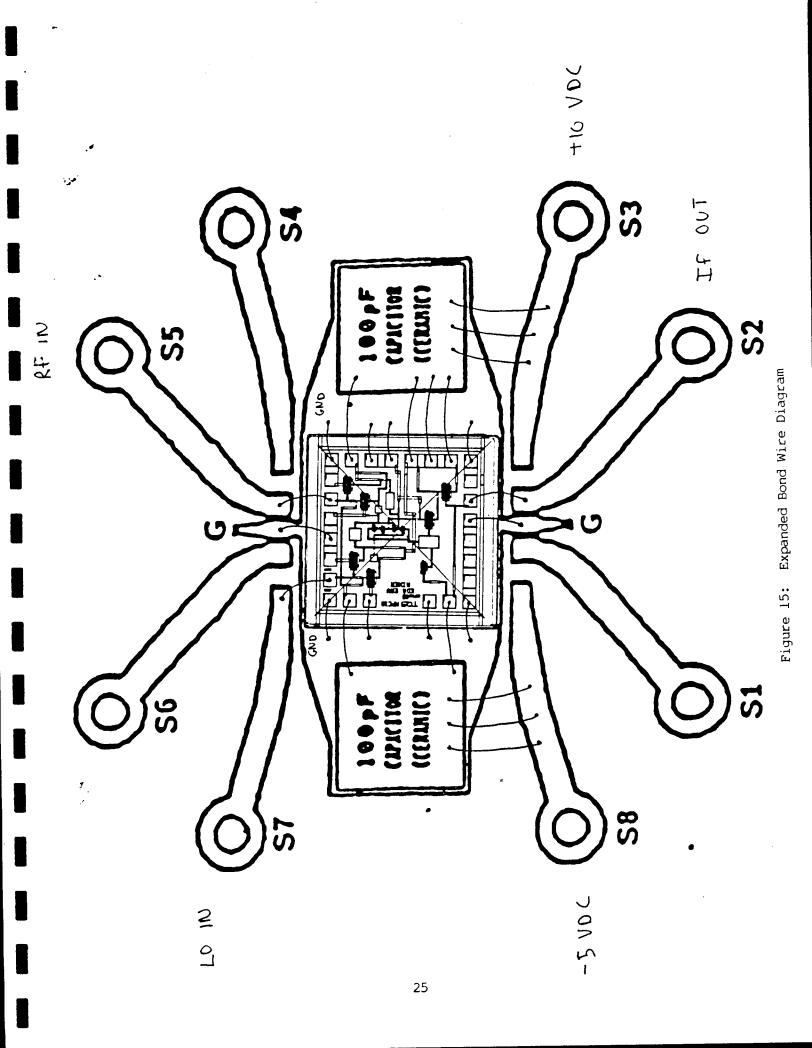

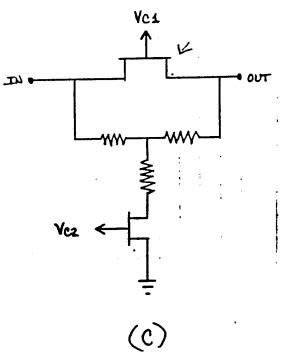

Bonding Diggram switched Attenuator

## ABSTRACT

This paper describes the design of a MMIC elliptic filter using active FET resonators. Resonators composed of passive MMIC components typically have Qs of less than twenty. Active resonators were designed with Qs of several hundred. High Q resonators enable the synthesis of high performance filter networks. This paper discusses the design of a 4 GHZ active elliptic filter.

## MMIC ELLIPTIC FILTERS

### INTRODUCTION

Gallium Arsenide Monolithic Integrated Circuit Technology is currently being applied to military sensors, survielance and communications systems to reduce size and weight. A typical receiver in any of these systems combines active components with filters. The filters reject unwanted signals and spurious products, increasing the system dynamic range.

At the present time most MMIC receiver designs use off-chip resonators and filters in the frequency conversion process. MMIC resonators have low Q and cannot be tuned during the manufacturing process. A smaller more reliable product would result if the filters were integrated into the chip with the other components.

This paper investigates the problems associated with the design of a 100% monolithic elliptic filter. The problem of low component Q is solved by introduciing FETs to create active resonators. Some of the problems associated with active filter design are identified and solved.

# CURRENT STATE OF THE ART

A review of MMIC designs in recent literature has revealed examples of monolithic filters. A MMIC mixer-lowpass filter combination was reported by Yang for use in a 6 GHZ to 10 GHZ receiver. Esfandiari<sup>2</sup> developed a two pole Chebyschev filter with 5% bandwidth. The best example of MMIC filter designs is reported by Halladay<sup>3</sup>. He developed a set of four wideband elliptic filters centered between 1.5 GHZ and 9.2 GHZ. These filters form the preselector for a electronic warfare system.

The filter networks discussed in these papers are implemented with passive MMIC components. Performance is limited by the low Q of passive resonators. The problem of low resonator Q has been solved by using active components. At video and HF frequencies operational amplifiers are used to create active filters. At this time no microwave Opamps are available. In the VHF/UHF range active resonators based on BJTs and lumped elements have been constructed (ref. 4-7,1969-83). The filter described in this paper operates in the microwave range using FETs and 100% monolithic construction.

### ELLIPTIC FILTER SYNTHESIS

The elliptic filter examined in this report is a 7 pole ladder network. The component values for the passive lumped element network are obtained from tables. The resulting network consisted of ten parallel LC resonators. Other topologies were not considered due to time constraints. This network provides a excellent example of the problems encountered in active MMIC filter design.

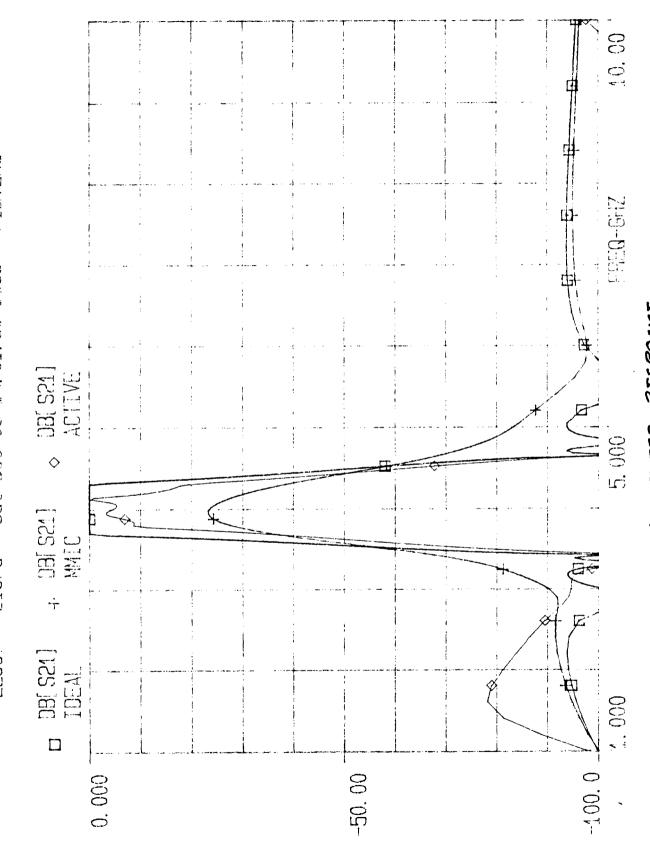

The response of this filter using ideal components and passive MMIC components is shown in figure 1.The "IDEAL" curve was generated using perfect inductors and capacitors. The "MMIC" curve was generated by substituting passive MMIC components into the network. The low Q of the MMIC resonators has clearly degraded the filter performance. This filter requires resonator Q > 140. The following Qs for 4 GHZ MMIC resonators were estimated by computer simulation.

| L (ph) | C (pf) | Q   |

|--------|--------|-----|

| 2000   | Ø.792  | 7.5 |

| 1000   | 1.583  | 7.5 |

| 5ØØ    | 3.16Ø  | 8.Ø |

The Q of the MMIC resonators must be increased by a factor of at least  $2\emptyset$  to implement the desired filter.

#### HIGH Q RESONATOR SYNTHESIS

Parallel RLC resonators are described by the following set of equations.

$$Y_{r} = 1/R + j(wC-1/wL)$$

$$w_{g}^{2} = 1/LC$$

$$Q_{g} = w_{g}CR = R/w_{g}L = R\sqrt{C/L}$$

Libra - Sat Dec 09 14:01:50 1989 - FILTER9 EEsof -

FIGURE 1: FILTER RESPONSE

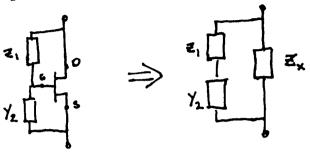

FETs may be used to synthesize high Q resonators by using the following technique.

$Z_{1}=R_{1}+jX_{1}$   $Y_{2}=G_{2}+jW_{2}$   $Z_{x}=(Z_{1}*Y_{2}+1)/g_{m}$   $Z_{x}=(1/g_{m})[(R_{1}G_{2}-X_{1}W_{2}+1)+j(G_{2}X_{1}+R_{1}W_{2})]$

Selection of suitable impedance values make it possible to drive the real part of Z negative. Shunting Z with a lossy conductance yields the following network conductance.

$Y_n = (G_z - G_x) + j(W_z + W_x)$

The real part of the resulting network can be zeroed yielding a reactive network with infinite Q.

Actual synthesis of MMIC resonators is not as easy as the math leads one to believe. As the network Q is increased the network becomes sensitive to parasitic effects, particularly stray capacitance. The possibility of negative resistance also creates the possibility of oscillation.

Approximately thirty different single and dual FET active resonator networks were investigated. Analysis was based on ideal components with finite Q. Simulations were performed using the available MMIC component library. Synthesizing a resonator with the required Q,  $w_g$  and L/C ratio is difficult. The optimizers used by Libra tend to optimize only one or two of the three required parameters yielding a useless network. Resonators 2 and 3 could not be accuratlly synthesized. Optimization is a problem that will have to be resolved in future investigations. The following results were obtained for the ten filter resonators.

| L (ph) | ) C (pf) | <sup>W</sup> Ø (ghz) | Q (MMIC) | <u>Q (active)</u> |

|--------|----------|----------------------|----------|-------------------|

| 261    | 6.080    | 3.989                | 15.9     | 885               |

| 27Ø4   | Ø.3Ø9    | 5 <b>.</b> Ø35       | 1.7      |                   |

| 5149   | Ø.588    | 2.891                | 5.4      |                   |

| 156    | 1Ø.17Ø   | 3.987                | 17.5     | 281               |

| 719    | 1.628    | 4.649                | 7.1      | 952               |

| 977    | 2.212    | 3.423                | 7.Ø      | 238               |

| 161    | 9.837    | 3.988                | 16.5     | 717               |

| 965    | 1.137    | 4.8Ø5                | 7.9      | 199               |

| 1400   | 1.65Ø    | 3.311                | 6.8      | 343               |

| 282    | 5.647    | 3.989                | 16.4     | 92Ø               |

Replacing the passive resonators with the active resonators yielded the network response labeled "ACTIVE" in figure 1. The circuit file containing the actual active resonator circuits is attached to this report.

The active resonator filter response approaches the ideal response. The deviation from ideal is caused by the active resonators not quite having the correct resonant frequencies and L/C ratio. Those two problems cause the filter poles to shift and the sections to mismatch. Yielding a distorted network response. This problem should be solvable if the optimizer can be made to work correctly. The active filter response has removed some of the passband loss and restored the narrow transition bands. Hence this design technique may yield usable filter networks after further research.

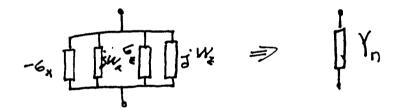

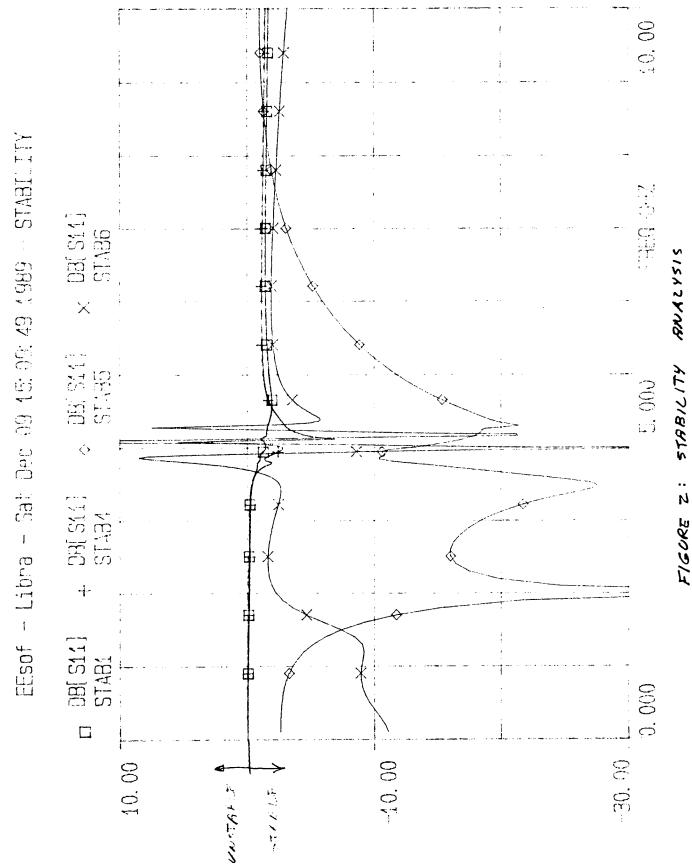

### STABILITY ANALYSIS

Introducing active components into the filter network creates the possibility of oscillation. The resonators themselves may oscillate or they may oscillate when connected to the network. The oscillation condition for a network node may be expressed as follows.

|S<sub>all</sub>S<sub>bll</sub>|>1 possible oscillation

It is interesting to note that even though a resonator may have gain the network may still remain stable if the correct feedback is not present at that node.

The following method of testing for oscillation using actual component models was developed.

```

CKT

... network a definition

DEF1P NetA

... network b definition

DEF1P NetB

PROC

STABILITY= NetA * NetB

OUT

STABILITY DB[S11]

```

Using this technique the stability of active resonators 1,4,5 and 6 were tested. The results shown in figure 2 indicate that resonators 4 and 6 are unstable and that resonators 1 and 5 are stable. This technique allows the network to be tested with actual component performance data and suitable layout parasitics. The circuit file used to generate this test is attached to this report.

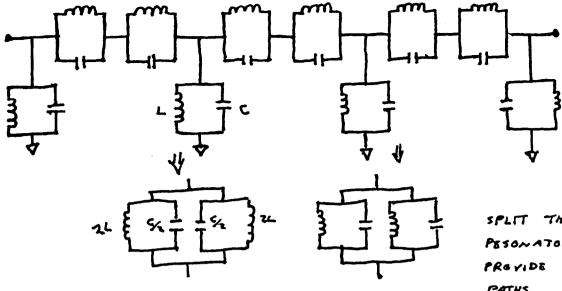

## BIASING

Active components require DC bias to operate. The DC needs to enter and exit the circuit at low impedance points, preferably AC grounds. The ladder filter topology does not provide a ground for every resonator. To solve this problem the following approach was going to be used. The active resonators would all use identical FETs ( lum x 600um) connected in series. The DC would enter and exit the circuit on the ground side of the shunt resonators. Gate biasing would be accomplished using a ladder of large value resistors. The expected schematic for this technique is developed in figure 3.

This design never progressed to the point of actually constructing this network and simulating the bias network effects on the filter response. However the active resonators selected were designed with this biasing technique envisioned.

Some of the dual FET resonators offered desirable performance if two types of FETs were used. However the biasing for multiple FETs some of which were floating would have been much more complicated and beyond the scope of this project. A more integrated approach would have been to use the dual FET resonators and balance the impedance transformations in each filter section to match biasing requirements.

STABILITY

SPLIT THESE PESONATORS TO 2 DC PATHS

### SUMMARY

The filter design attempted in this paper was not successful. Analysis showed that the resulting network was not a high performance filter, but a poorly designed oscillator. However several successes were made. High Q resonators were synthesized and analysis techniques were developed. It appears that active MMIC filters are possible to design using single FETs and monolithic components. Further research is required to optimize resonator design and filter topology. MMIC filters will enable the design of a new generation of monolithic receivers. REFERENCES

1. D.C. Yang, R. Esfandiari, T.S. Lin, T. O'Neill, "Wideband GaAs MMIC Receiver," 1987 IEEE MTT-S Digest, p.93-95

2. R. Esfandiari, D. Maki, M. Siracusa, "Design of Interdigitated Capacitors and Their Application to Gallium Arsenide Monolithic Filters," MTT January 1983, p.57-64

3. R.H. Halladay, A. M. Pavio, S.D. Bingham, A. Kikel, "A Monolithic Channelized Preselector for EW Receiver Applications," 1988 IEEE MTT-S International Symposium Digest, p.573-578

4. Adams, MTT Sept. 1969, p.662

5. Snyder, MTT Jan. 1970, p.2

6. Flinyuk, Radio Engineering Electron Physics, Vol. 28 Jan. 1970

7. Kapilevich, Radio Engineering, Vol. 40 No. 2. May 1983

8. A. Zverev, "handbook of Filter Synthesis," Wiley