### Fall 2008 JHU EE787 MMIC Design Student Projects Supported by TriQuint, and Applied Wave Research Professors John Penn and Dr. Michel Reece

Medium Power Amplifier—Matt Crowne Phase Shifter C-band – Mitesh Patel Mixer S-Band – Brendan McElrone Power Amplifier C-band – Ben Brawley Low Noise Amplifier – Minhaj Raza Small Signal Amplifier – Tom Pierce Power Amplifier C-band – D. Durachka Volt. Cont. Osc. C-band – Kang Yuan

Matthew Crowne 525.787 MMIC Design Fall 2008 Instructor: John Penn C-Band Low Power PA

#### Abstract

A C-Band power amplifier for lower power applications was designed using the Triquint GaAs MMIC library and Applied Wave Research's Microwave Office design environment. The amplifier consists of two cascaded stages and is intended maximizes efficiency over other design parameters. The amplifier is centered at 5.5 GHz and achieves 38% power added efficiency and 20 dB of Gain across a +/- 200 MHz bandwidth with 9 dBm output power.

#### Introduction

A single ended C-Band power amplifier was designed for maximum efficiency on a Triquint MMIC process. The amplifier consists of two stages utilizing enhancement mode GaAs PHEMTS with on-chip matching networks. The driver stage has a gate periphery of 16um and is biased class AB. The final stage has 72um of gate periphery and is biased deep class B. The design is intended to run off a single 3.3V supply and has internal bias circuitry to produce the gate voltage. In Addition, separate gate pads are provided that can both check the bias points of the PHEMTs or, if necessary supply gate bias. This design allows maximum flexibility for prototype development.

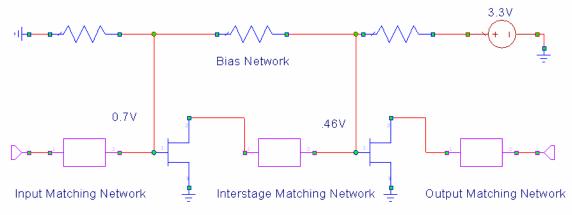

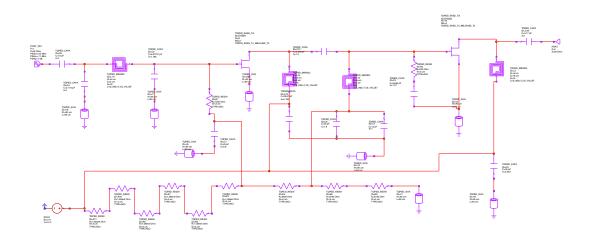

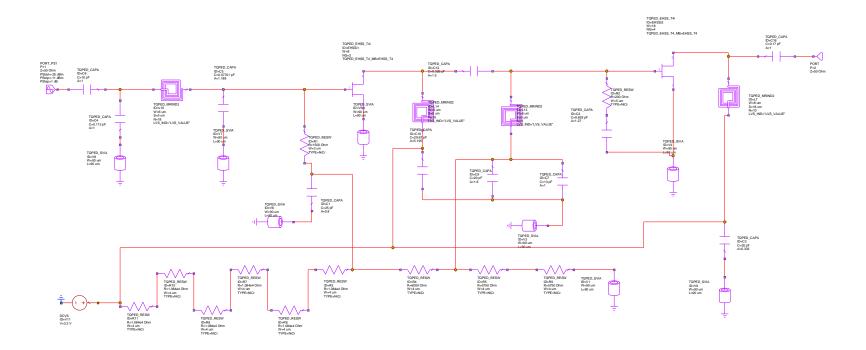

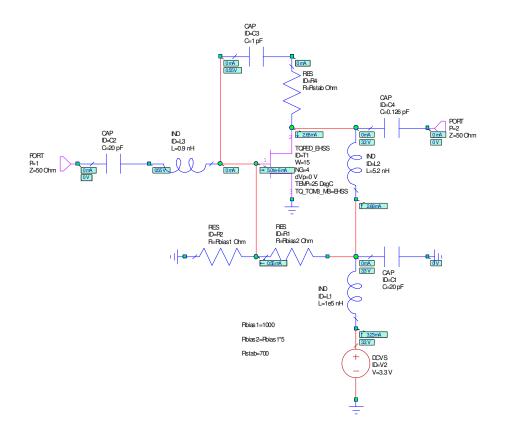

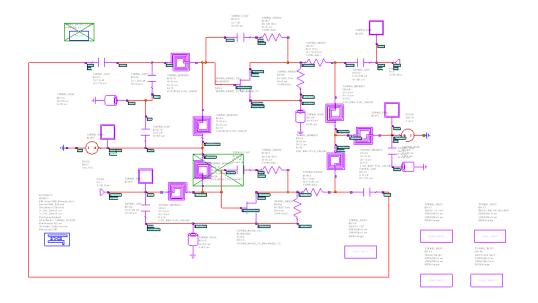

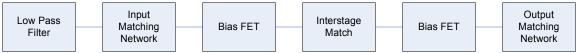

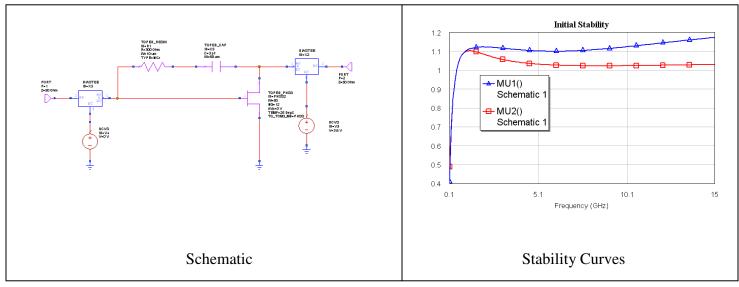

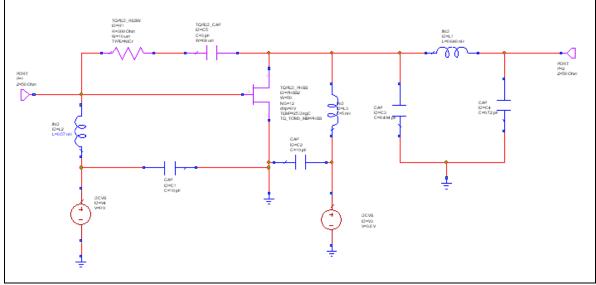

A simplified schematic is shown in Figure 1. The output matching network was designed to maximize efficiency. The interstate match also had to be designed for gain and efficiency, while the input match could focus on increasing gain.

**Figure 1. – Simplified Schematic**

Table 1 summarizes key performance parameters across the operating bandwidth.

| Frequency | Pout | Gain  | PAE   |

|-----------|------|-------|-------|

| GHz       | dBm  | dB    | %     |

| 5.3       | 9.58 | 20.39 | 38    |

| 5.5       | 9.89 | 20.74 | 43.25 |

| 5.7       | 9.26 | 20.15 | 40.27 |

**Table 1. - Key Performance Parameters**

#### **Design Approach**

The amplifier was designed to maximize efficiency for a low power application. The metrics used to design this amplifier are summarized in Table 2

|               | Spec               | Goal                                  |

|---------------|--------------------|---------------------------------------|

| BW:           | 5.3 Ghz-5.7GHz     |                                       |

| Pout:<br>PAE: | 9 dBm<br>>40%at fc | 10 dBm<br>40% across the<br>bandwidth |

| Gain Ripple:  | +/- 0.5            | +/- 0.5                               |

#### Table 2. – Specifications and Goals

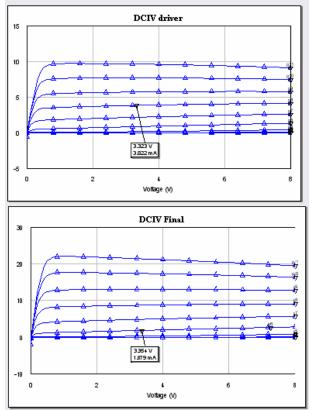

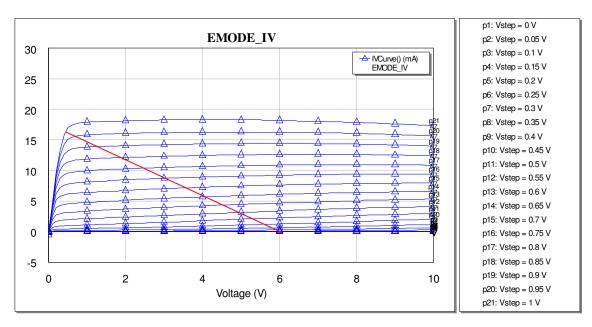

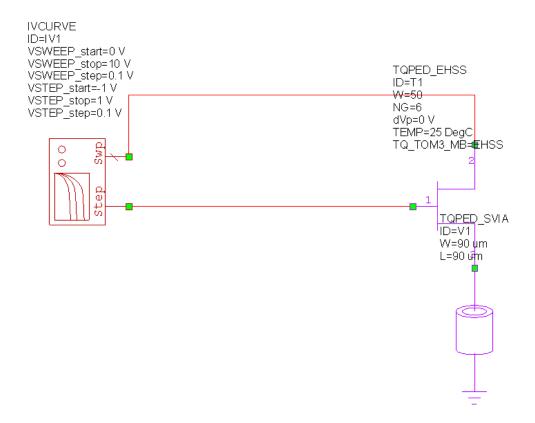

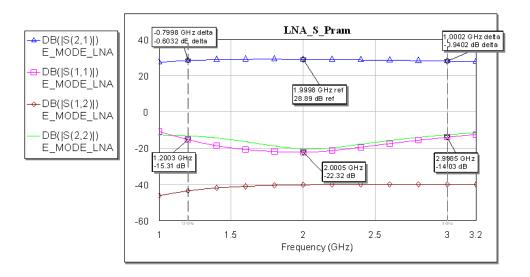

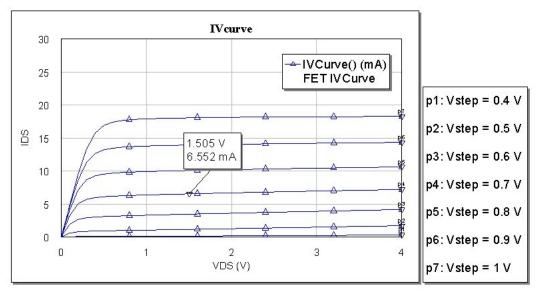

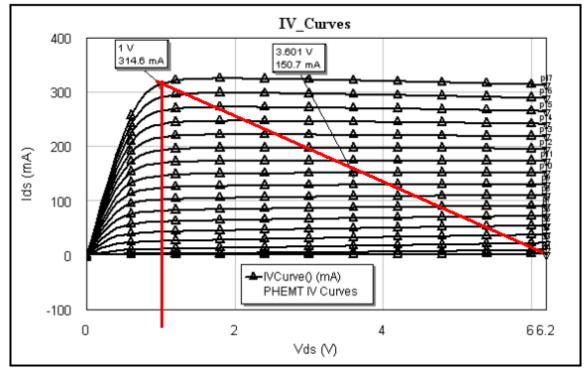

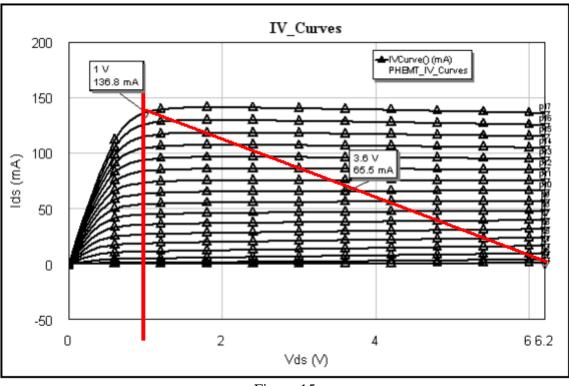

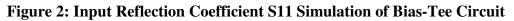

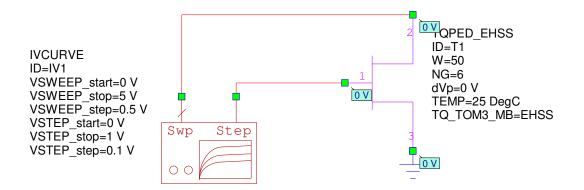

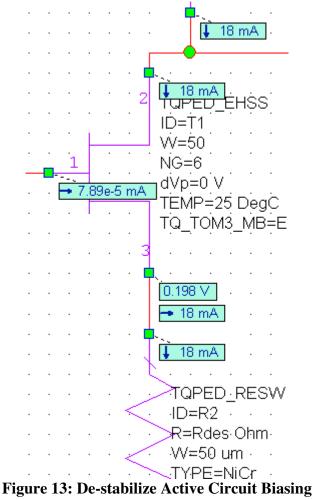

Several approaches were investigated for meeting these specifications. Approaches that seemed promising early in the design phase utilized class-F or some other high efficiency technique. However, such an approach requires more components then a traditional matching network. Ideal simulations that appeared promising quickly lost their appeal when the low quality inductors inherent with Triquint and other GaAs MMIC processes. When the results reduced to efficiencies that are achievable with a deep class B approach the simpler matching networks they offered became more attractive. The DCIV plots are shown in Figure 2. For the driver stage Vgs = 0.7V and for the final stage Vgs = 0.5V. These values were tuned in the final design

**Figure 2 – DCIV curves**

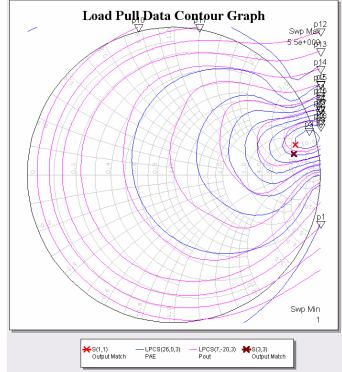

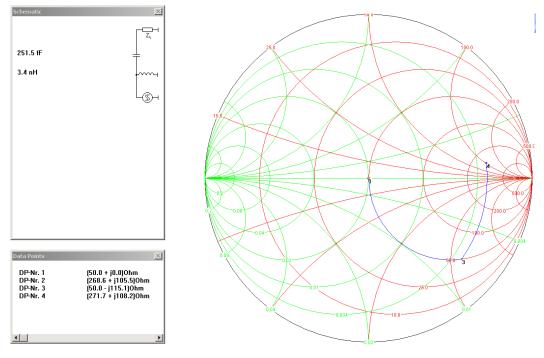

As a deep class B bias excluded a Cripps method approach to determining optimum output load, a load-pull simulation was performed on the output FET model. The load pull contours are shown in figure 3 for 5.5 GHz. The simulated ideal output matching network is indicated with the red "x" and the maroon "x" is the output match from the finalized layout.

Figure 3 – Load Pull and Matching Networks

The best match for both the PAE and Pout are located on the edge of the smith chart, this is a product of the deep class B bias on the devices means that the match that will be limited in bandwidth. As the design is meant to maximize PAE at the center frequency (with a goal of extending that over +/- 200 MHz) this will still be suitable for our design. The match was achieved with a shunt inductor-series cap combination that also provides a drain voltage insertion and a DC block on the output of the MMIC.

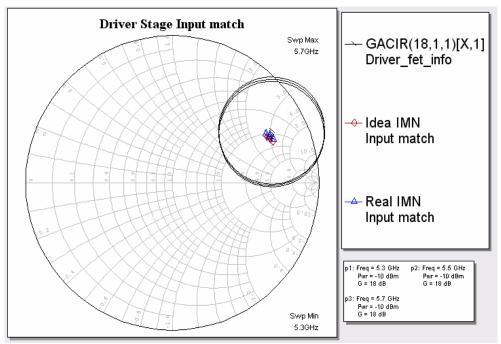

Next, the input matching network for the first stage was designed for the driver stage. The IMN was designed to provide the maximum gain available. Figure 4 shows the available gain circles and the results of the IMN simulation. The design would be revisited for final tuning after the layout was near completion.

The interstate matching network was the final component to be designed. In an interstate matching network, the output of the driver stage is matched to the input of the final stage without having an intermediate 50 ohm match in between. A shunt inductor series capacitor pi pad topology was chosen to achieve this match and allow convenient bias insertion for the drain of the driver and the gate of the final stage.

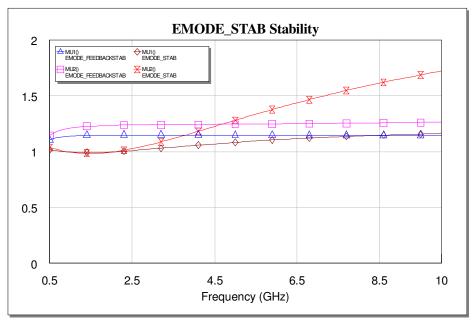

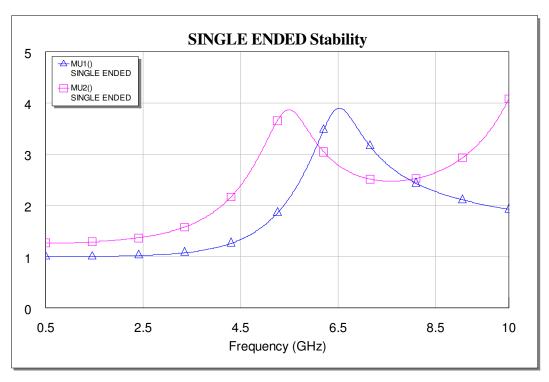

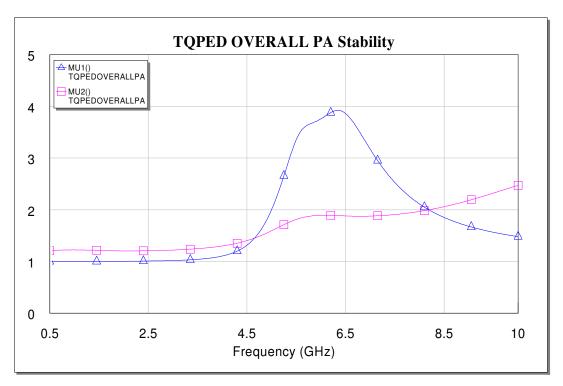

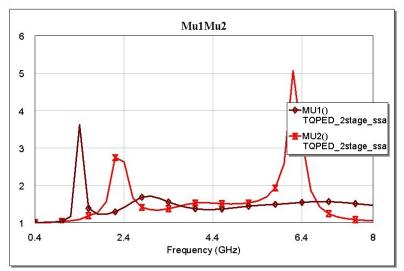

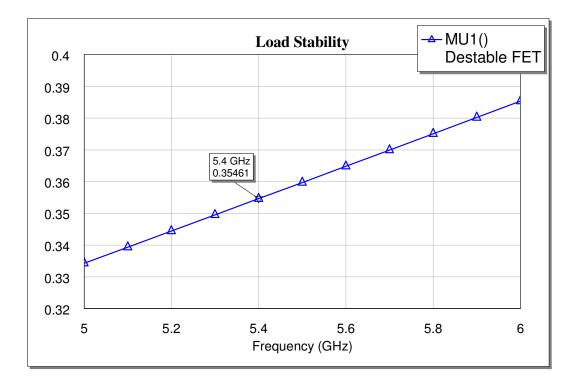

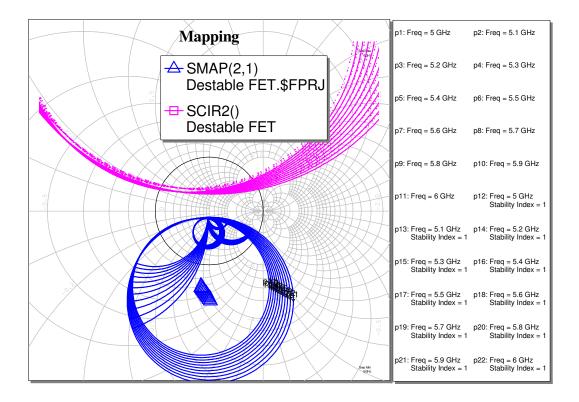

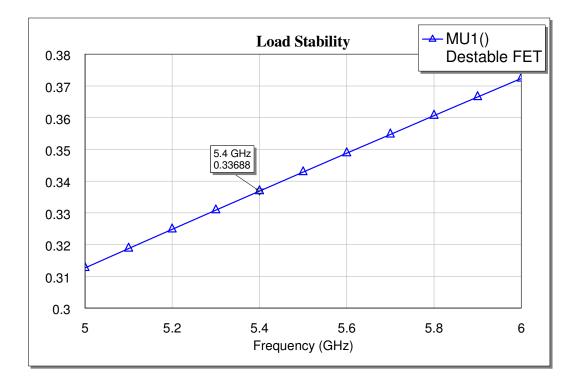

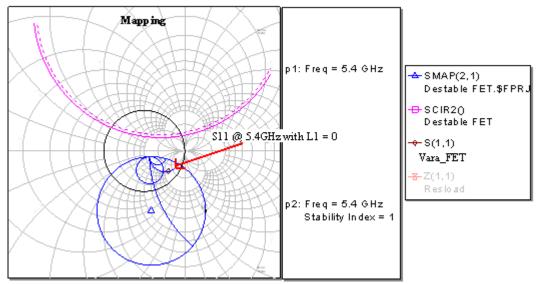

Figure 4. – Available gain circles and input match for the driver stage

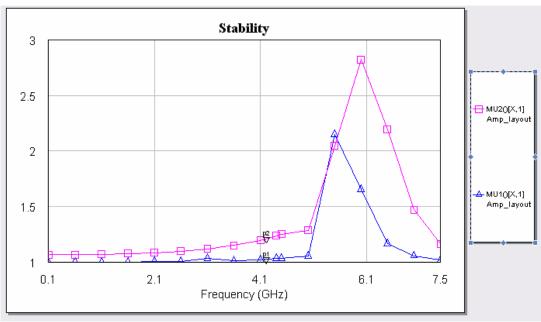

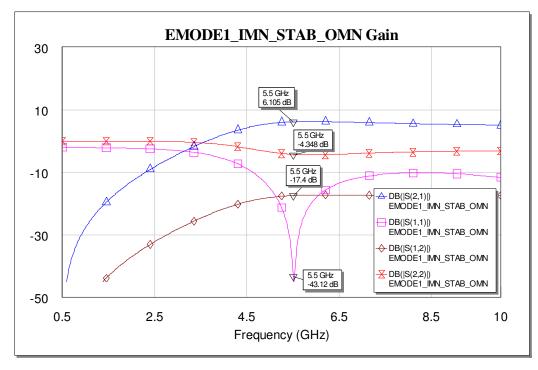

The design is stabilized with a shunt resistor on the power device with a large cap to ground. In this location the resistor will not dissipate significant RF power and the DC blocking cap to ground ensures no DC power dissipates in the resistor. It was decided not to put a stabilizing resistor onto the driver stage as a significant amount of gain was lost with the addition of the 200 ohm resistor on the final. The combined amplifier has an input and output mu value greater then 1 and with 50 ohm terminations the amplifier should not oscillate. Figure 5 shows the stability factor over frequency.

Figure 5.-Stability factor for the final design

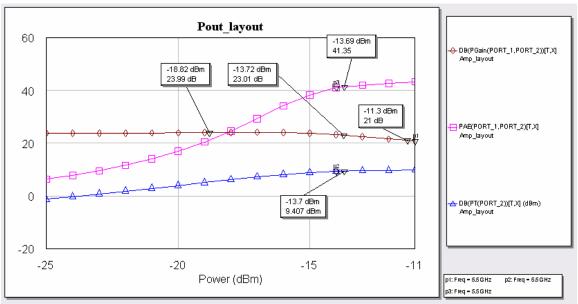

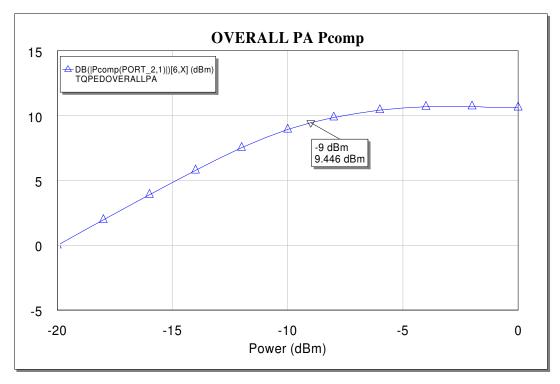

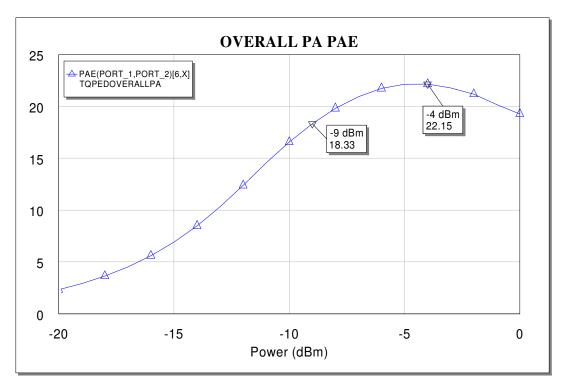

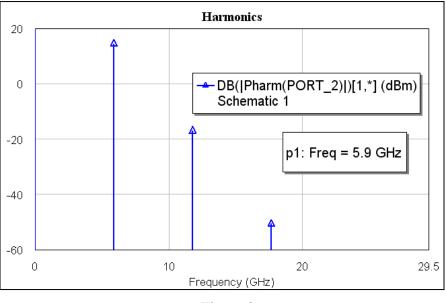

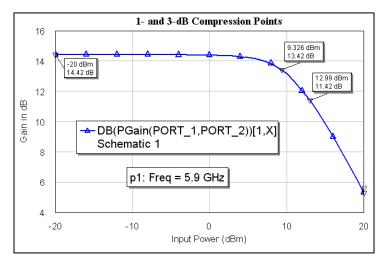

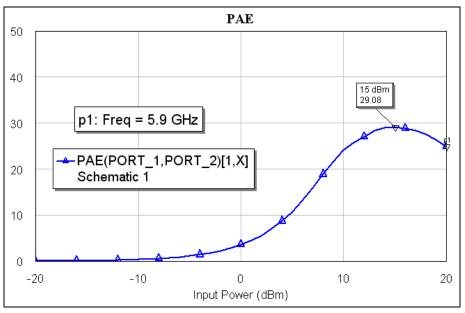

Figures 6 and 7 shows the combined amplifiers performance after the layout was finalized. Figure 6 shows the amplifiers power output, PAE and power gain as the input power is increased at the center frequency of 5.5 GHz.

Figure 6 – Pout, PAE and Gain vs. Pin

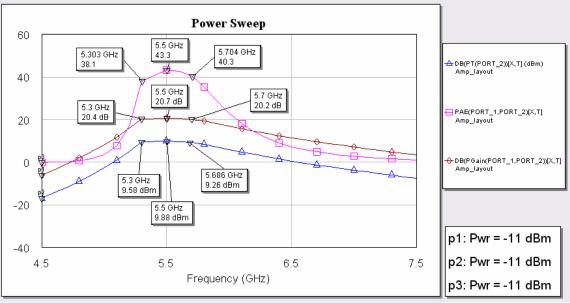

Figure 7 shows a power sweep with a fixed Pin. When driven properly 38% PAE is achieved as is a Pout greater then 9 dBm with 20 dB of gain from 5.3 GHz to 5.7 GHz.

**Figure 7 – Pout vs. Frequency**

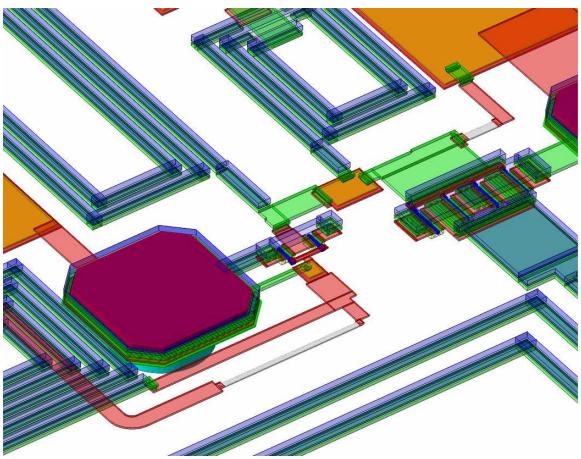

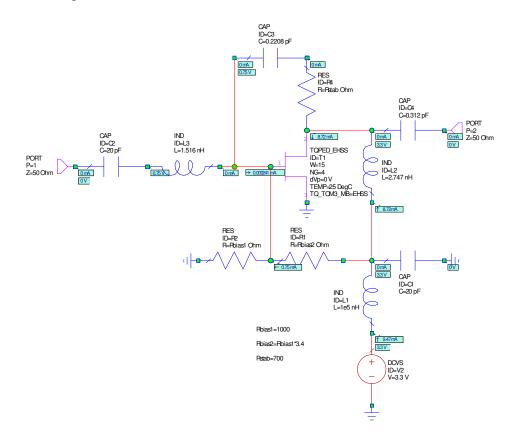

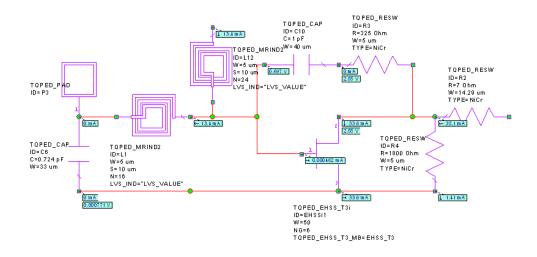

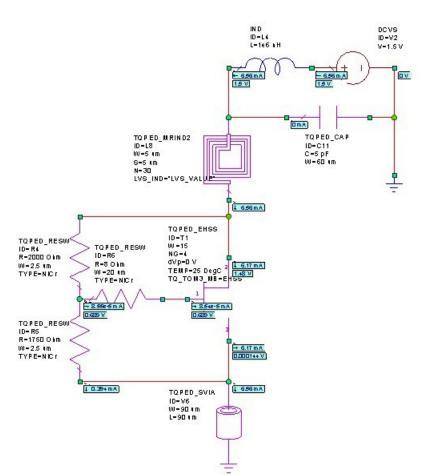

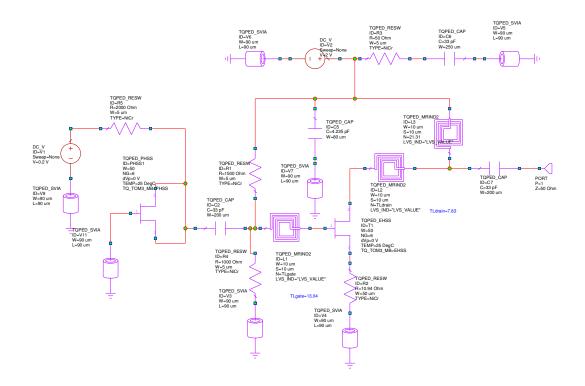

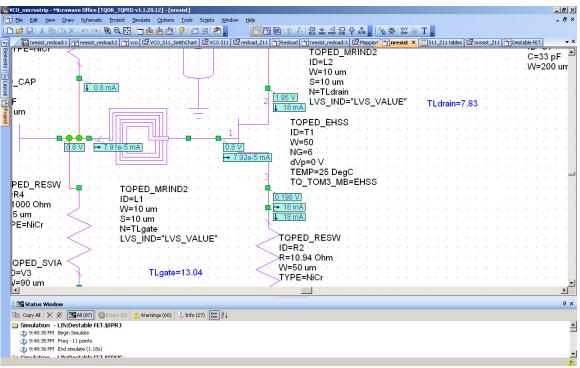

The simplified schematic is presented below in figure 8. The simulated data presented here used AWR's transmission line models on the Triquint substrate that have been removed for clarity, see Appendix A for the full schematic. From left to right are the amplifier's input matching network, driver stage, interstage matching network, final stage, and the output matching network. The bias network runs along the bottom of the amplifier.

**Figure 8 – Amplifier Schematic**

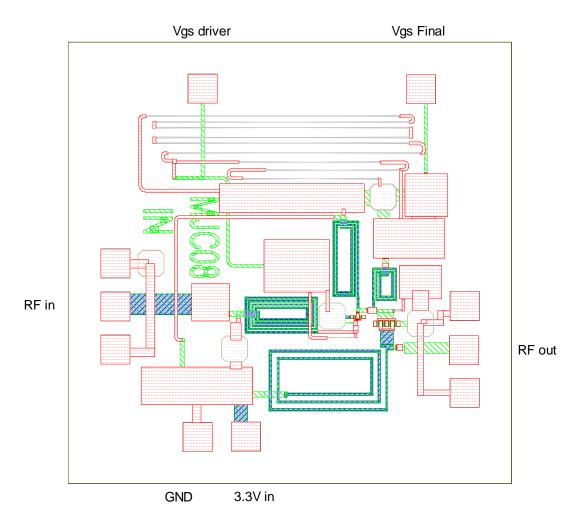

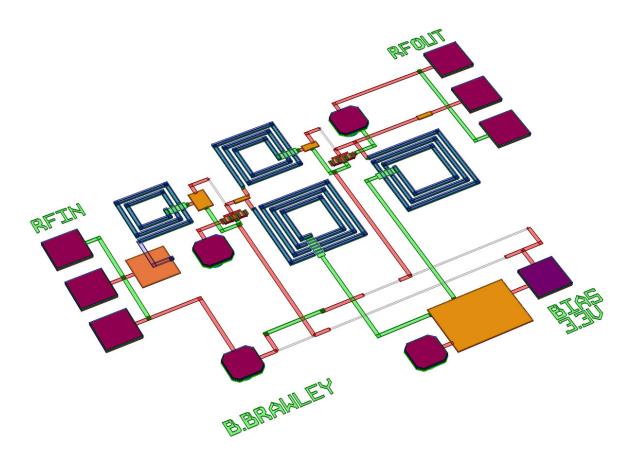

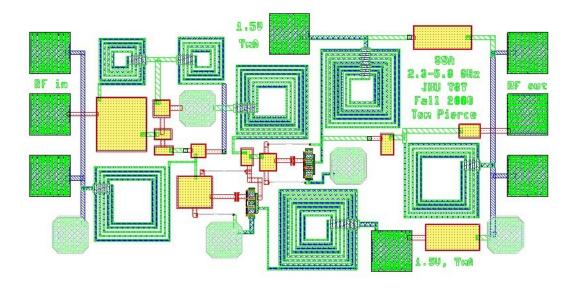

The layout is shown in figure 9. The input is at the bottom of the chip and the output is at the top. The RF ports use ground-signal-ground ports for maximum RF performance. To the left are the supplementary gate bias ports. On the right hand side is the main power pin and a supplemental ground pin as well. Layout successfully passed ICED design rule check before submission to Triquint.

Figure 9 – Amplifier MMIC Layout

#### **Test Plan**

Test equipment needed:

- 1. Agilent 8510 Network Analyzer (or equivalent)

- 2. Agilent E3632A power supply (or equivalent)

- 3. Agilent 34410A DMM (or equivalent)

- 4. Agilent 8683Bsignal generator (or equivalent)

- 5. Agilent E4416A power meter (or equivalent)

- 6. Agilent 8480Power sensor (or equivalent)

The Amplifier should be connected to a 3.3 V power supply which has been current limited to 20 mA. As the design consists of PHEMTs and contains internal bias circuitry there is not the concern of damaging the devices if there is not gate bias applied before the drain bias.

Test procedure:

1. With no RF source applied, power on DUT power pin with 3.3V and record quiescent current:

\_\_\_\_ mA (approximately 3 mA)

2. Set logic analyzer so that Pout < -20 dBm and frequency from 2.5 GHz to 7.5 GHz. Record the small signal gain and the small signal S11 and S22.

| <br>S11 |

|---------|

| <br>S22 |

| S21     |

This will verify the general health of the amplifier as well as check that the design is centered at  $5.5~\mathrm{GHz}$

3. Set the signal generator for -20 and 5.3 GHz and perform the following measurements (Grayed cells are calculated parameters.)

| Pin = -20 dBm |      |      |         |  |  |  |

|---------------|------|------|---------|--|--|--|

| Frequency     | Pout | Gain | Current |  |  |  |

| GHz           | dBm  | dB   | mA      |  |  |  |

| 5.3           |      |      |         |  |  |  |

| 5.5           |      |      |         |  |  |  |

| 5.7           |      |      |         |  |  |  |

| 1 dB compression Measurements |             |      |          |         |              |     |  |  |

|-------------------------------|-------------|------|----------|---------|--------------|-----|--|--|

| Frequency                     | Pin at P1dB | P1dB | Gain @P1 | Current | Pcomsumption | PAE |  |  |

| GHz                           | dBm         | dBm  | dB       | mA      | mW           | %   |  |  |

| 5.3                           |             |      |          |         |              |     |  |  |

| 5.5                           |             |      |          |         |              |     |  |  |

| 5.7                           |             |      |          |         |              |     |  |  |

| 3 dB compression Measurements |             |      |          |         |              |     |  |  |

|-------------------------------|-------------|------|----------|---------|--------------|-----|--|--|

| Frequency                     | Pin at P3dB | P3dB | Gain @P3 | Current | Pcomsumption | PAE |  |  |

| GHz                           | dBm         | dBm  | dB       | mA      | mW           | %   |  |  |

| 5.3                           |             |      |          |         |              |     |  |  |

| 5.5                           |             |      |          |         |              |     |  |  |

| 5.7                           |             |      |          |         |              |     |  |  |

#### Conclusions

A C-Band power amplifier was designed that achieves greater then 38% efficiency and 9 dBm out with 20 dB of gain across 400 MHz of bandwidth. All design specifications were achieved. Due to the design tradeoffs to maximize efficiency not all of the design goals were achieved, a summery of the simulated performance is given in table 4.

|                 | Spec               | Goal                     | Simulated | Measured |

|-----------------|--------------------|--------------------------|-----------|----------|

| BW:             | 5.3 Ghz-<br>5.7GHz |                          |           |          |

| Pout:           | 9 dBm              | 10 dBm                   |           |          |

| PAE:            | >40%at fc          | 40% across the bandwidth |           |          |

| Gain<br>Ripple: | +/- 0.5            | +/- 0.5                  |           |          |

Table 4. - Specs, goals, and worst case measured parameters

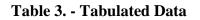

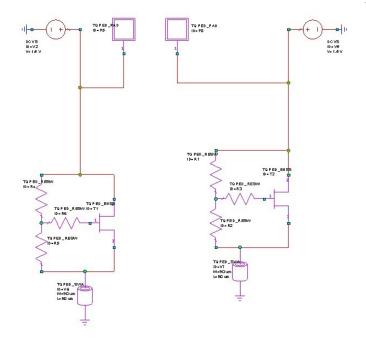

Figure 10. – close up of the transistors

### **APENDIX A – Schematic Views Full Schematic**

### Simplified Schematic

"Swami Shreeji"

# MMIC EE787 Final Report C-Band 3Bit Phase Shifter Fall 2008

**By: Mitesh Patel**

# **Table of Content**

| <u>1.Abstract3</u>         |

|----------------------------|

| 2.Introduction             |

| 3.Design Approach          |

| a.Specification vs. Goals4 |

| b.Tradeoffs4               |

| 4.Simulations              |

| 5.Schematic7               |

| a.Switch Schematic7        |

| b.RF Schematic7            |

| c.DC Schematic8            |

| 6.Layout Plot8             |

| 7.Test Plan9               |

| 8.Summary & Conclusions    |

| Appendix A                 |

# 1. Abstract

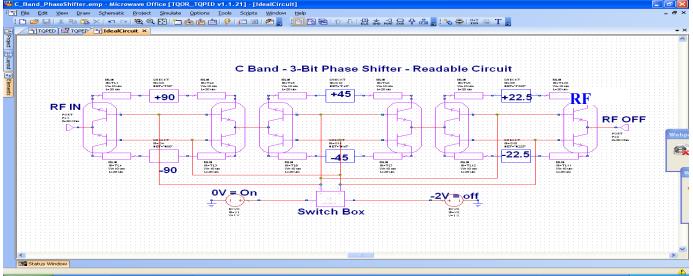

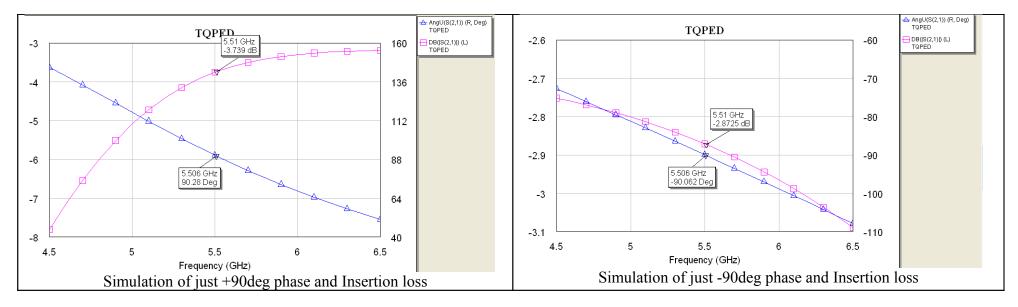

This report talks about C- Band 3bit phase shifter designed using Microwave Office from AWR inc. and Triquient's TQPED library for a MMIC design. Each bit is switched between +/-22.5, +/-45, and +/-90 giving relative phase shift from 0 to 360deg in 45deg increment at center frequency of 5.5Ghz. The design was layout on 60mil x 60mil AnaChip.

# 2. Introduction

A 3-bit phase shifter is a circuit element used in many applications, especially in Radar. A phase shifter takes RF signal in and output same RF signal but at different phase. In radar application, by changing the phase of signal, you can steer the beam of antenna in different angle without physically moving the antenna. Hence, you can scan a wide region without even moving the antenna. By changing the phase rapidally, one can change the direction of beam digitally at very fast rate. Here, Phase shifter plays a key roll.

# 3. Design Approach

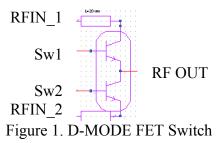

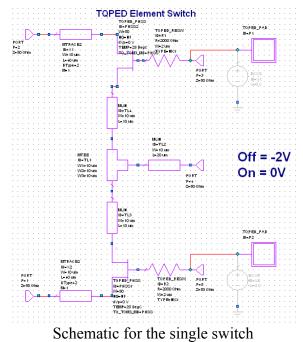

As shown above, each bit of phase shifter has two FET switches, which switches either of two inputs (RFIIN1 or RFIN2) to RF Output and vise versa. Another word, depending on voltage applies to Sw1 and Sw2, RF1 is connected to RF OUT or RF2 is connected to RF Out.

Figure 2. Single Bit circuit.

When we combine two switches with circuit which lead or leg phase by certain amount, we get 1bit phase shifter, as shown above. In figure 2a, when switches are connected to top circuit (hence bottom switch off) we get Phase lead by certain amount. When both bottom switch on (top switch off), we get phase leg by certain amount. Right side and left side, top and bottom switch are tie together so they switched simultaneous and act like one switch, as shown in figure 2b. Switching is controller by applying 0v to turn it on, and -2V to turn it off and it is done digitally.

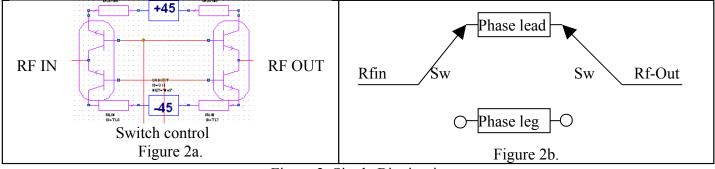

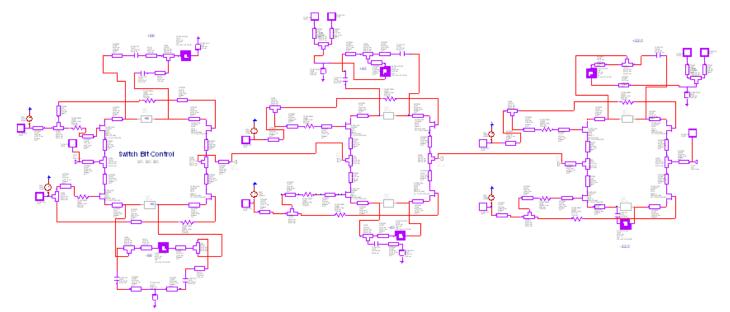

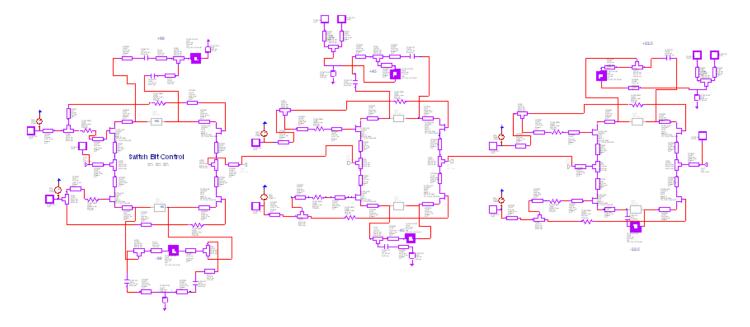

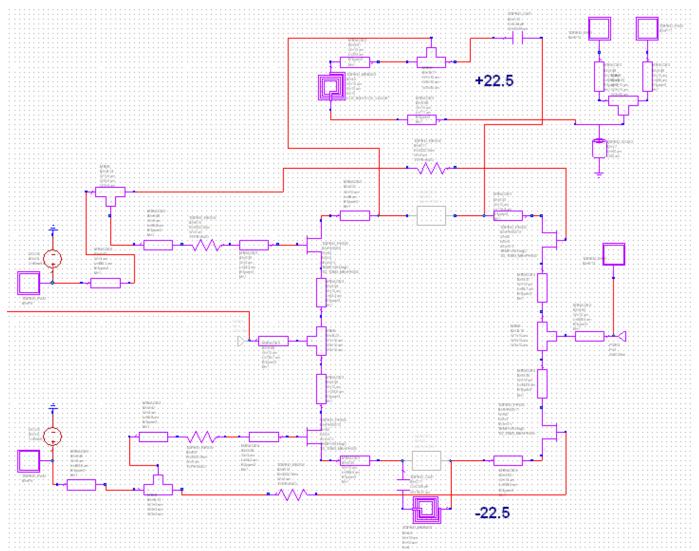

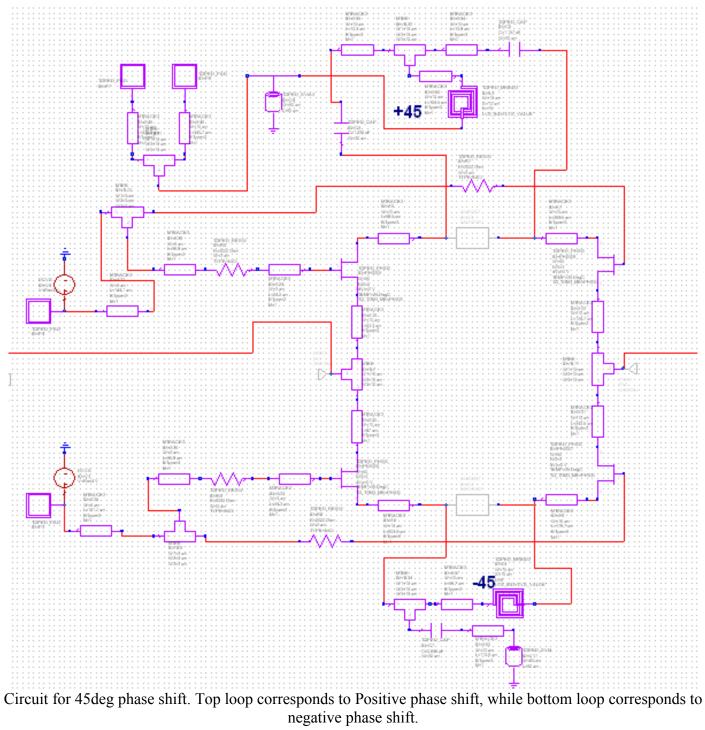

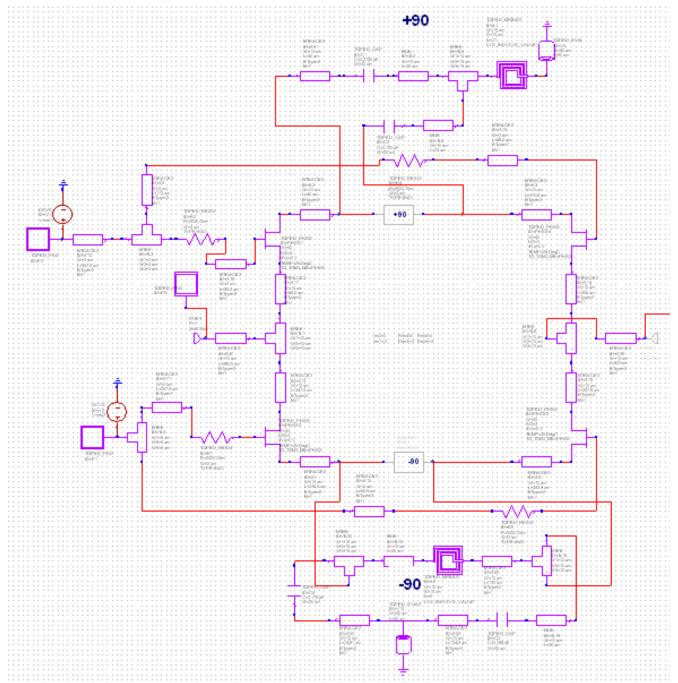

Once we connect the circuit for all the 3-bit, the final circuits looks like what's shown in figure 3 below. Each switch for each bit (lead or leg) is control by switch box, which switch it on (0V) or off (-2V). At any given time, there either phase Lead or leg part of the circuit is on but not both. That gives either +/- X amount of phase from each bit. When we combine three such phase bit, we get following 3-bit phase shifter circuit.

Figure 3. 3-bit Phase shifter switching circuit

Each of the phase bit are made of capacitor and/or inductor. Inductor leads the phase from capacitor. We have used pi network (series cap, shunt inductor and series cap) to get the lead part of the phase and another pi network (shunt cap, series inductor and shunt cap) to get the leg part the phase. Then each element are tuned until we got the desire phase of +/-22.5, +/45, and +/-90 deg.

| Criteria       | Goal                         | Simulation Results  |

|----------------|------------------------------|---------------------|

| Frequency      | 5150 to 5875 MHz             | 5150 to 5875 MHz    |

| Bandwidth      | > 725 MHz                    | > 725 MHz           |

| Insertion Loss | <6 dB min IL                 | < 11dB              |

| Phase shift    | Step 45, 90 and 180          | Step 45, 90 and 180 |

| VSWR, 500hm    | <1.5:1 input & Output        | <2:1 input & Output |

| Supply Voltage | 0 to +3.3 volts switch input | 0v and -2V          |

| Size           | 60 x60mil ANACHIP            | 60 x60mil ANACHIP   |

## a. Specification vs. Goals

## b. Tradeoffs

In designing 3-bit phase shifter, there are two main tradeoffs. One is number of fingers in D-FET (3 vs. 6). 3 finger FET gives you better isolation (-20dB) and less space, however, less current carrying capability. 6 fingers gives you more current carrying capability but worst isolation (-10dB) and requires more space. We use 3 finger for our design approach. 2<sup>nd</sup> trade was in size of inductor. If we make inductor bigger, the separation between turn increase and give better insertion loss. However it requires more space, we have many inductors in our circuits. In our design, we kept size of inductor small to fit every thing in 60mil by 60mil circuits at cost of few more dB of

insertion loss. After fitting everything on layout, we notice that we had space to increase the size of inductor, but due to lake of time, were not able to do it

#### ▲ AngU(S(2,1)) (R, Deg) TQPED TQPED -6 50 ↔ DB(|S(2,2)|) (L) TQPED 5.5 GHz -8.619 dB DB([S(2,1)]) (L) -8 20 TQPED <u></u>∠DB(|S(1,1)|) (L) TQPED -10 -10 5.5 GHz -21.17 Deg -12 -40 5.5 GHz -12.14 dB -14 -70 5.5 GHz -14.32 dB -16 -100 5 6 4.5 5.5 6.5 Frequency (GHz)

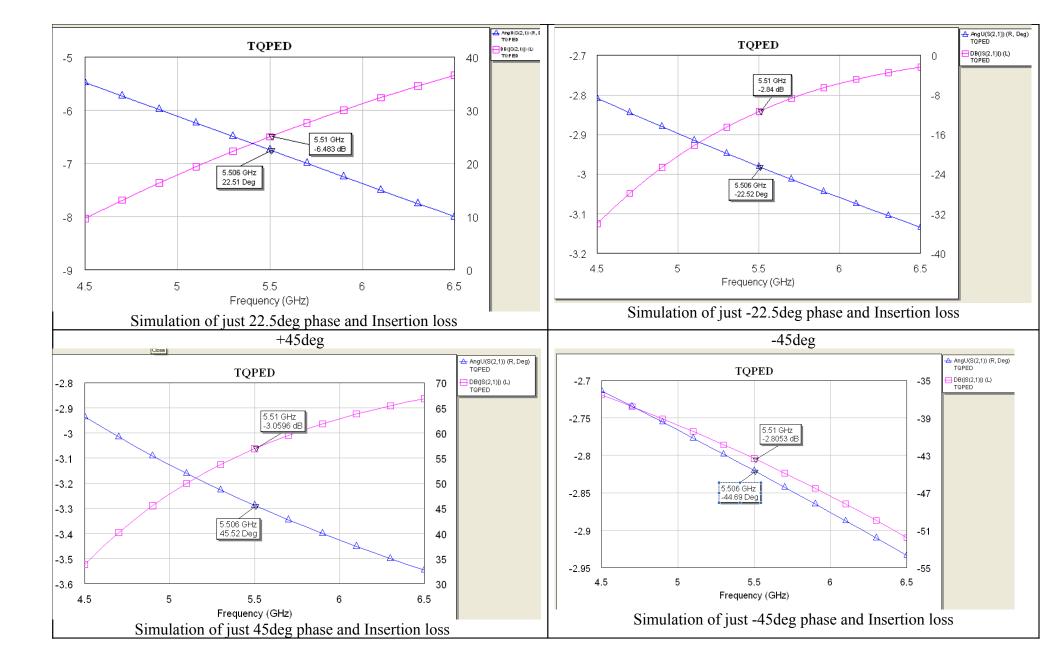

# 4. Simulations

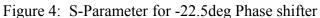

Figure 4 shows, S-parameter of -22.5deg when first bit is set to -90, second bit to +45 and last bit to +22.5, hence -22.5deg simulation results were obtained. Insertion loss of -8.6dB is expected since capacitor and inductor are lossy element.

Figure 5: S-Parameter for 157.5deg Phase shifter

Figure 5 shows, the S-Parameter for 157.5 (-202.5+360 = 157.5) deg phase shift. This is achieved by setting  $1^{st}$  bit to +90, second bit to +45 and last bit to +22.5deg. Insertion loss of 8.77dB is expected out all three bit.

| Similar to 157.5 and -22.5 deg simulation above, rest of the results were obtain and recorded below for all the |

|-----------------------------------------------------------------------------------------------------------------|

| combination of the 3-bit phase shifter (lead and leg)                                                           |

|        | Simulated Phase Results                                                               |                 |                                      |                        |                   |         |                         |

|--------|---------------------------------------------------------------------------------------|-----------------|--------------------------------------|------------------------|-------------------|---------|-------------------------|

| Eac    | h 3 bit i<br>Phas                                                                     | ndividual<br>se | Calculated Results Simulated Results |                        | Results           |         |                         |

| 90     | 45                                                                                    | 22.5            | Absolute<br>Phase(deg)               | Relative<br>phase(deg) | S21<br>Phase(deg) | S21(dB) | Delta<br>Phase<br>(deg) |

| 1      | 1                                                                                     | 1               | 157.5                                | 315                    | 159.8             | -8.7775 | 2.3                     |

| 1      | 1                                                                                     | -1              | 112.5                                | 270                    | 107               | -9.57   | 5.5                     |

| 1      | -1                                                                                    | 1               | 67.5                                 | 225                    | 61.79             | -11.23  | 5.71                    |

| 1      | -1                                                                                    | -1              | 22.5                                 | 180                    | 22.61             | -11.328 | 0.11                    |

| -1     | 1                                                                                     | 1               | -22.5                                | 135                    | -21.17            | -8.62   | 1.33                    |

| -1     | 1                                                                                     | -1              | -67.5                                | 90                     | -70.64            | -9.07   | 3.14                    |

| -1     | -1                                                                                    | 1               | -112.5                               | 45                     | -116.5            | -9.63   | 4                       |

| -1     | -1                                                                                    | -1              | -157.5                               | 0                      | -158.4            | -10.1   | 0.9                     |

| 90deg  | 90deg bit equal 1 corresponds to +90 (0v Vgs), while -1 corresponds to -90 (-2vs Vgs) |                 |                                      |                        |                   |         |                         |

| Absol  | Absolute Phase Example> 157.5 = 90*1 + 45*1 + 22.5*1                                  |                 |                                      |                        |                   |         |                         |

| Relati | ve Phas                                                                               | se = Absolu     | te Phase + 157.5                     |                        |                   |         |                         |

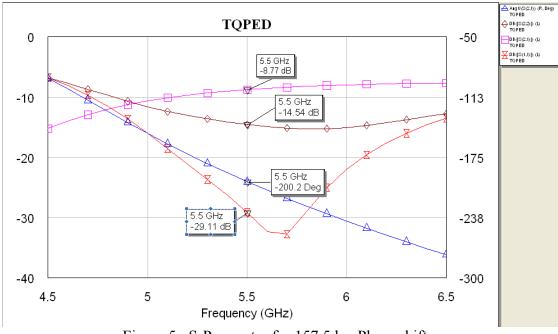

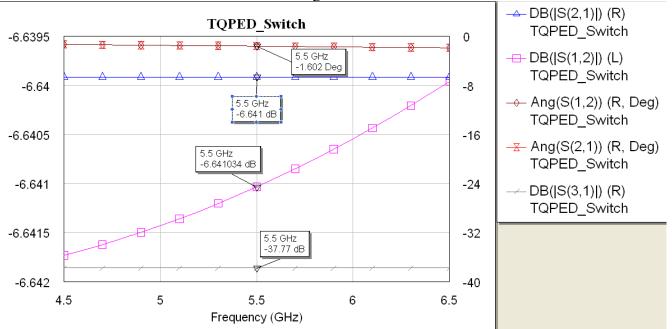

Similar to whole phase shifter circuit above, following figure shows S-Paramater for just single switch shown in figure 1.

For just single switch, insertion loss between RFIN 1 and RFOUT is -6.6dB, and phase offset of 1.6deg. Isolation between RFIN2 and Output is -37dB.

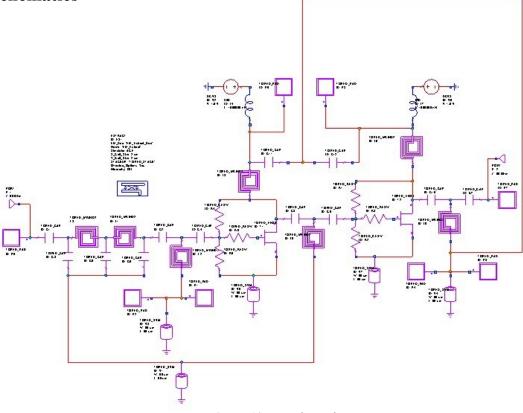

# 5. Schematic

### a. Switch Schematic

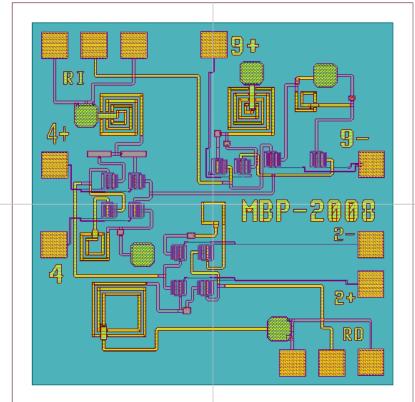

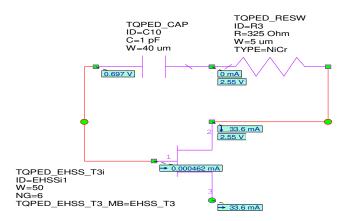

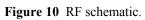

Above is final RF schedule for 3bit Phase shifter, which has all the switches and phase shift bit. Left circuit is 90deg bit, middle is 45deg bit, and at the end is 22.5deg bit. All the top part is for positive phase shift (lead), all the bottom corresponds to negative phase shifts (leg). To see detail of any phase shift bit, please refer to schematic in appendix.

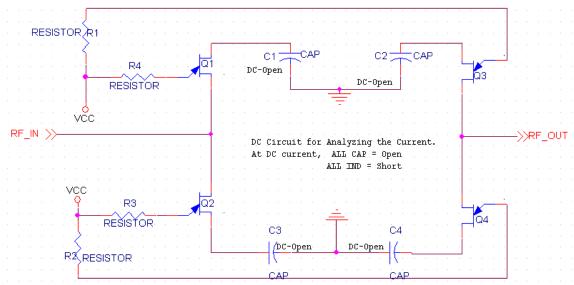

Above circuit shows DC current simulation of single bit. All Capacitor acts as open in DC, and all inductor (not shown) act as DC short.

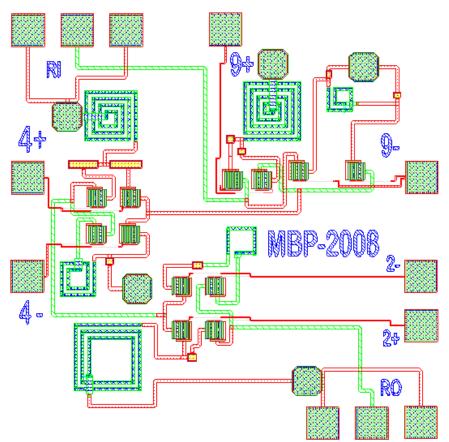

# 6. Layout Plot

Above is layout for the final 3-bit phase shifter circuit. RF input is located at (RI) top-left handside with Ground-Signal-Ground pas. RF output (RO) is located in the bottom right hand side with Ground-Signal-Ground pads.

Rests of pads are for the switch, where we can apply, 0v or -2v to switch on/off. 0V turn on it, and -2V turn it off. 4+ reference to 45deg phase shifter bit. 9- reference to 90deg phase shifter bit, and 2+ reference to 22.5deg phase shifter bit.

# 7. Test Plan

- Calibrate the network work analyzer for 4.5 to 6.5GHz in 10Mhz step. Place marker at 5.15 GHz, 5.5 GHz and 5.875 GHz.

- Apply 0V or -2V to all pads labeled (4+, 4-, 9-, 9+, 2-, or 2+)

- Connected GSG probe from Network analyzer port 1to RF input pads label 'RI'.

- Connect GSG probe from Network analyzer port 2 to RF Output pads label 'RO'.

- Measured Phase and magnitude of S21 and record it on table above

- Switch the voltage to next configuration on table below and re-measured the phase and magnitude

- When done measuring, disconnect, turn off all the equipment.

- Finally compare measured results verse simulation.

|        | Measured vs. Simulated Results Comparsion |        |                     |                        |                |         |                   |  |  |

|--------|-------------------------------------------|--------|---------------------|------------------------|----------------|---------|-------------------|--|--|

| Each   | 3 bit vo                                  | ltage  | Measu               | red results            | Simulated Re   | esults  |                   |  |  |

| 90     | 45                                        | 22.5   |                     |                        |                |         |                   |  |  |

| (9+/-) | (4+/-)                                    | (2+/-) | Absolute Phase(deg) | Absolute Magnitude(dB) | S21 Phase(deg) | S21(dB) | Delta Phase (deg) |  |  |

| 0V     | 0V                                        | 0V     |                     |                        | 159.8          | -8.7775 |                   |  |  |

| 0V     | 0V                                        | -2V    |                     |                        | 107            | -9.57   |                   |  |  |

| 0V     | -2V                                       | 0V     |                     |                        | 61.79          | -11.23  |                   |  |  |

| 0V     | -2V                                       | -2V    |                     |                        | 22.61          | -11.328 |                   |  |  |

| -2V    | 0V                                        | 0V     |                     |                        | -21.17         | -8.62   |                   |  |  |

| -2V    | 0V                                        | -2V    |                     |                        | -70.64         | -9.07   |                   |  |  |

| -2V    | -2V                                       | 0V     |                     |                        | -116.5         | -9.63   |                   |  |  |

| -2V    | -2V                                       | -2V    |                     |                        | -158.4         | -10.1   |                   |  |  |

# 8. Summary & Conclusions

The C-band phase shifter was designed very close to specification. As seen in table 1, phase shift accuracy exceeded specification requirement (worst case of 5deg off from target). All three bits were fitted in 60mil by 60mil layout. Insertion loss in this design was exceeding the requirement value because of smaller inductor size use and too many transmission lines instead of using single line with routing tool.

With more time, following can be improve in this design

- Add circuit to use +3.3 and 0v for source switching control

- Try to reduce the insertion loss by

- Make all the inductor little bigger and retune each

- Avoid series component as much as possible

- Look into the possibility of using E-mode transistor for any improvement

- Simulate RF structures in a EM simulator to find out unwanted coupling or interaction between parts.

# Appendix A

a. Final RF Schematic & Results

Above is final RF schedule for 3bit Phase shifter. Left circuit is 90deg bit, middle is 45deg bit, and at the end is 22.5deg bit. All the top part is for positive phase shift, all the bottom corresponds to negative phase shifts. Detail of each 3 bits circuit is given below.

Circuit for 22.5deg phase shift. Top loop corresponds to Positive phase shift, while bottom loop corresponds to negative phase shift.

Circuit for 90deg phase shifter. Top loop corresponds to Positive phase shift, while bottom loop corresponds to negative phase shift.

Different view of the layout Chip Page 15 of 15

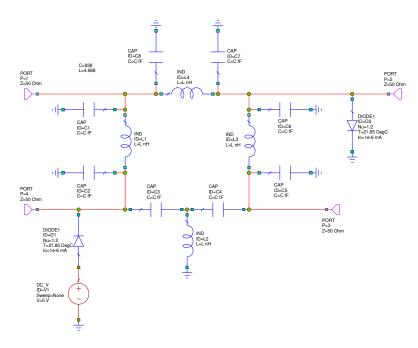

# S-Band Up/Down Mixer EE 525.787 – MMIC Design Fall 2008

Prepared by: Brendan McElrone

### Abstract

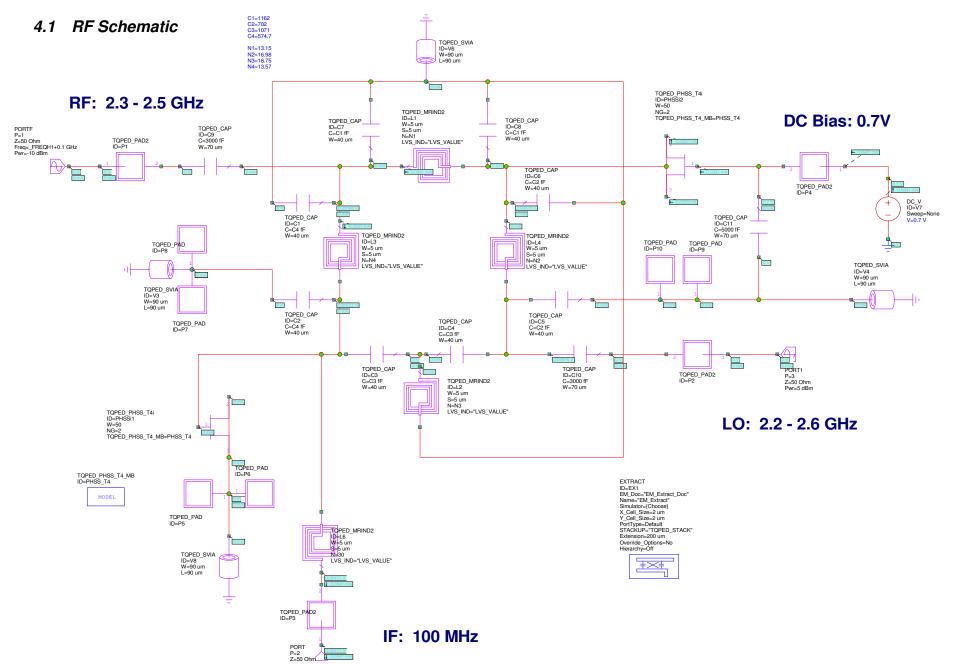

The following report details a monolithic microwave integrated circuit (MMIC) S-Band up/down mixer design. The mixer was designed for a radio frequency (RF) input range of 2.3 – 2.5 GHz. The local oscillator (LO) design frequencies range from 2.2 – 2.6 GHz with an up/down-converted intermediate frequency (IF) of 100 MHz. Based off a rat-race coupler design, the s-band mixer incorporates TriQuint modeled PHEMT transistors as switching diodes. Design simulations verified acceptable results: conversion loss less than 9 dB, RF/LO isolation greater than 20 dB, voltage standing wave ratio (VSWR) better than 2.5:1. The mixer meets all design requirements at an LO power of +4dBm with optimal performance at +7dBm.

### 1 Introduction

With intentions of creating a configurable S-band duplex transceiver, an up/down mixer was designed to cover the wireless communications service (WCS) and industrial, scientific, and medical (ISM) frequencies. The up/down mixer incorporates a 180° lumped element rat-race coupler with diode configured transistors. An ideal lumped element model of the design is shown in Figure 1.

Figure 1: Ideal lumped element S-band up/down mixer

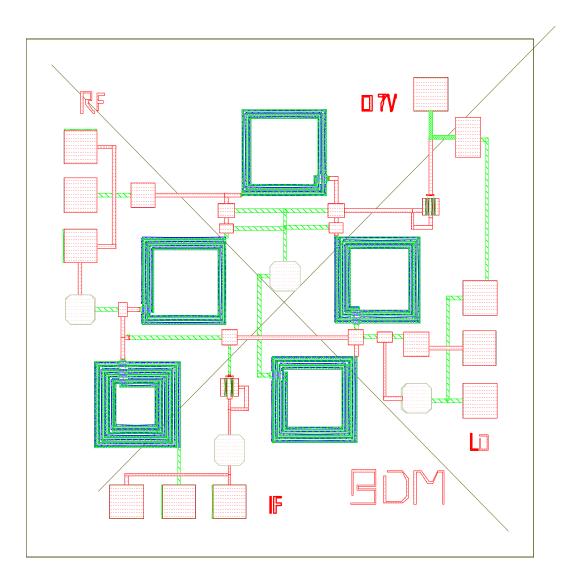

The mixer RF frequencies range from 2.3 - 2.5 GHz and the LO frequencies range from 2.2 - 2.6 GHz. The design targeted a maximum LO power of +7dBm with simulations showing a functional design at +4dBm. Simulations demonstrate conversion loss approximately 8dB, RF/LO isolation approximately 25dB, and a VSWR ranging from

1.2:1 - 2.3:1. A layout file was designed around a 60x60mil TriQuint anachip. Tradeoffs were made between layout size and circuit design for optimal performance characteristics.

# 2 Design Approach

As a subsystem of a configurable duplex transceiver, requirements must be specified prior to design implementation. Table 1 outlines these requirements.

| Mixer<br>Property | Minimum<br>Requirement                 | Design<br>Goal                 |

|-------------------|----------------------------------------|--------------------------------|

| RF frequency      | 2.305 – 2.497 GHz                      | 2.3 – 2.5 GHz                  |

| LO frequency      | 2.305 – 2.497 GHz<br>2.205 – 2.397 GHz | 2.3 – 2.5 GHz<br>2.2 – 2.6 GHz |

| IF frequency      | 100 MHz                                | 100 MHz                        |

| Isolation (RF/LO) | 10 dB                                  | 16 dB                          |

| LO power          | +7 dBm                                 | 0 dBm                          |

| VSWR              | 2.5:1                                  | 1.5:1                          |

| Conversion Loss   | 10 dB                                  | 7 dB                           |

Table 1: S-band up/down mixer design requirements

Several design steps were taken in order to effectively design a mixer meeting all of the predefined requirements. An ideal model of the rat-race coupler was designed followed by a TriQuint element based design. Upon optimizing the coupler, the diode configured PHEMT devices were incorporated into both the ideal and non-ideal models. Optimization was performed on the switching diode mixer designs. A layout file was then created and a final optimization was performed through layout property extraction. These steps are detailed in the following sections.

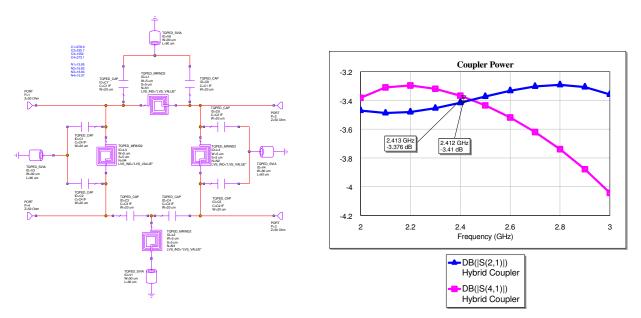

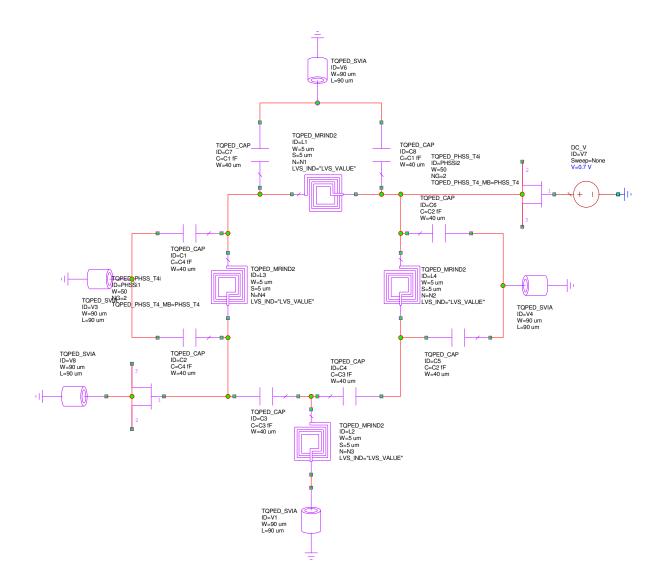

### 2.1 Rat-race Coupler Design

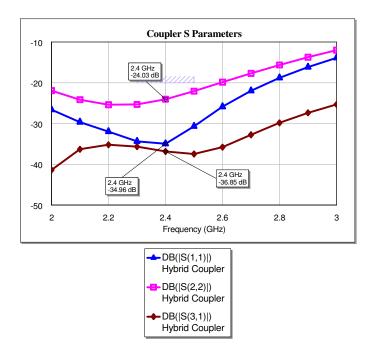

The 180° rat-race coupler was designed with both ideal and non-ideal components. In order to optimize the coupler, an equivalent power split between the coupling ports is desired. Additionally, theoretical phase requirements are desired. Figure 2 shows the non-ideal model with optimized coupled power. The non-ideal phase measurements were within the desired range.

Figure 2: Non-ideal rat-race coupler (left), non-ideal coupled power (right)

### 2.2 PHEMT Diode Configuration

The TriQuint PHEMT devices were optimized to reduce the effect on the rat-race coupler when incorporated into the design. In order to function as a diode, the PHEMT drain and source terminals were connected and acted as the diode cathode. The gate terminal was used as the anode. Ideally, the diode should look like a 50 ohm terminal when introduced into the coupler. In order to simplify the design, PHEMT width dimensions and finger count of 50 um and 2 respectively were used. Without implementing a diode matching network, these dimensions control optimization of the diode match. A direct current (DC) bias voltage source was used to reduce the overall LO drive power needed to turn the diodes on and off. The 0.7V bias was optimized in the final design.

### 2.3 Mixer Design

The diode configured PHEMT devices were incorporated into the coupler design to create the up/down mixer configuration. One diode was placed from coupler port 4 (anode) to ground (cathode). The other diode was configured from DC bias (anode) to coupler port 2 (cathode).

The initial mixer design approach was geared toward isolation optimization. Sparameters of the mixer were optimized during this process. Final design configurations were tuned to meet all requirements. Figure 3 shows the optimized S-parameters.

Figure 3: Optimized S-band mixer s-parameters.

#### 2.3.1 RF/LO/IF Isolation

With an ideal coupler based mixer design, the IF port can be inserted into the design in several configurations yet have no effect on performance. In order to do this, a large series inductor was used between the IF port and the other mixer circuitry.

In order to isolate the DC bias from the RF and LO ports, large series blocking capacitors were inserted between the RF/LO ports and the other circuitry.

### 2.4 Trade-offs

Many of the design trade-offs were a result of the 60x60mil area constraint. The RF/LO blocking capacitors were optimized for performance yet limited to reduce area consumption. Similarly, the inductor dimensions were limited.

Another trade-off involved the PHEMT diode circuitry. Introducing diode matching networks would enhance the performance of the mixer. Due to area constraints, the matching circuitry was left out of the design and the transistor dimension optimization was used to best match the device.

# 3 Simulations

| Table 2: Simulated results summary |                      |                        |  |

|------------------------------------|----------------------|------------------------|--|

| Mixer<br>Property                  | Simulated<br>Results | Minimum<br>Requirement |  |

| Isolation (RF/LO)                  | > 25 dB              | 10 dB                  |  |

| LO power                           | +4 dBm               | +7 dBm                 |  |

| VSWR                               | 1.2:1 – 2.3:1        | 2.5:1                  |  |

| Conversion Loss                    | ~ 8 dB               | 10 dB                  |  |

A summary of the simulated results are shown in Table 2.

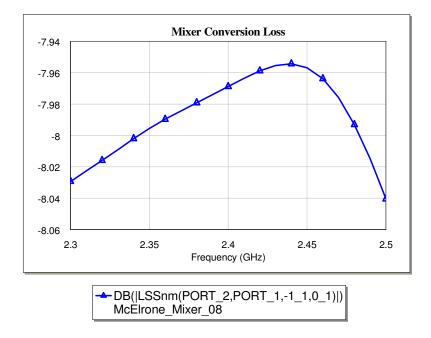

### 3.1 Conversion Loss

Figure 4: S-band up/down mixer conversion loss

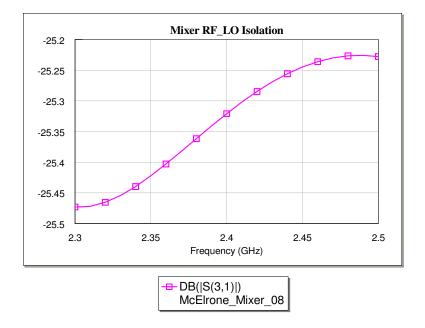

### 3.2 RF/LO Isolation

Figure 5: S-band up/down mixer RF/LO isolation

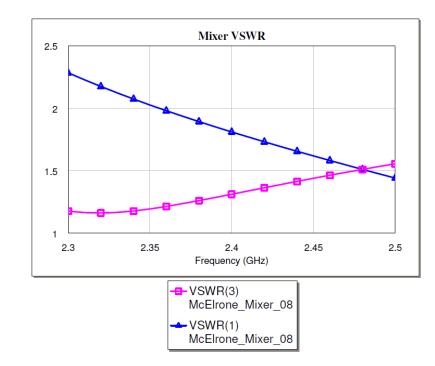

#### 3.3 VSWR

Figure 6: S-band up/down mixer VSWR

### 3.4 IF Spectral Analysis

#### 3.4.1 Up Mixer

#### 3.4.1.1 High Band

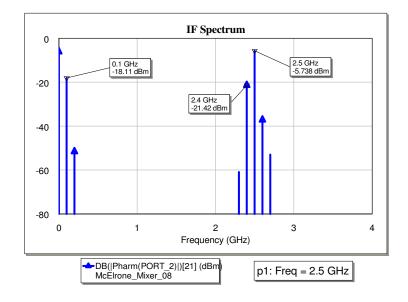

Figure 7: IF spectrum, mixer in high band of up mixer mode

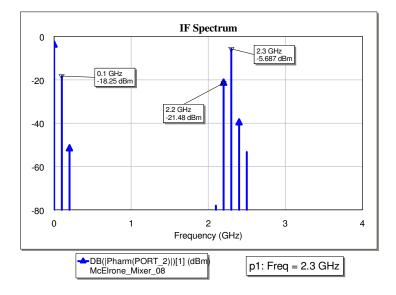

### **3.4.1.2** Low Band

Figure 8: IF spectrum, mixer in low band of up mixer mode

## 3.4.2 Down Mixer

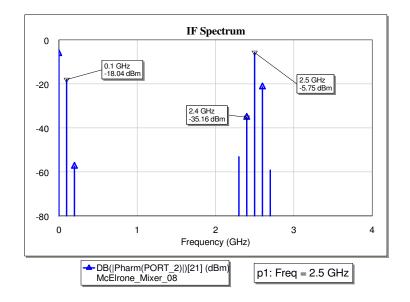

## 3.4.2.1 High Band

Figure 9: IF spectrum, mixer in high band of down mixer mode

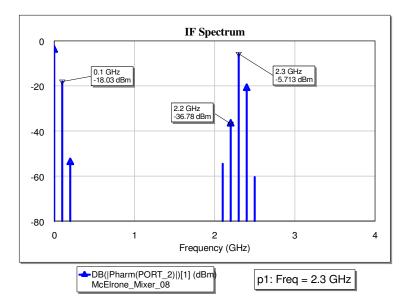

#### 3.4.2.2 Low Band

Figure 10: IF spectrum, mixer in low band of down mixer mode

## Schematic

## 4.2 DC Schematic

Figure 11: S-band up/down mixer DC schematic

## 5 Layout

Figure 12: S-band up/down mixer layout

## 6 Test Plan

## 6.1 S-parameter Testing

- 1. Connect network analyzer to the appropriate ports. Use RF as port 1 and LO as port 2. Setup to sweep from 2.3 2.5GHz.

- 2. Terminate IF port into a 50 ohm load

- 3. Apply 0.7Vdc to the DC bias terminal

- 4. Measure the s-parameters

## 6.2 Up Mixer Testing

- 1. Connect a signal generator to the LO port. Setup to sweep from 2.2 2.4 GHz in 0.05GHz increments. Set power output to +7dBm.

- 2. Connect a signal generator to the IF port. Set the frequency to 100MHz. Set power output to -10dBm.

- 3. Connect a spectrum analyzer to the RF port

- 4. Apply 0.7Vdc to the DC bias terminal

- 5. Measure RF output power at each LO frequency

## 6.3 Down Mixer Testing

- 1. Connect a signal generator to the LO port. Setup to sweep from 2.2 2.6 GHz in 0.05GHz increments. Set power output to +7dBm.

- 2. Connect a signal generator to the RF port. Setup to sweep from 2.3 2.5 GHz in 0.05GHz increments. Set power output to -10dBm.

- 3. Note: Keep the RF and LO signals consistent with a 100MHz IF output signal

- 4. Connect a spectrum analyzer to the IF port

- 5. Apply 0.7Vdc to the DC bias terminal

- 6. Measure the 100MHz IF output power at each frequency interval

## 7 Summary and Conclusions

As detailed in the document, the S-band up/down mixer met all design requirements. Optimizing the rat-race coupler circuitry was beneficial to the overall performance of the mixer. The design was successfully optimized for the area constraint. With the addition of diode matching networks, the mixer performance could be further optimized. The DC bias source effectively reduced the LO input power requirement.

# A 3.3V, C-Band GaAs MMIC Two-Stage Single-Ended Power Amplifier

by

**Benjamin Brawley**

A Design Project submitted in fulfillment of the requirements for

EE 787 MMIC Design

JOHNS HOPKINS UNIVERSITY

December 8, 2008

#### ABSTRACT

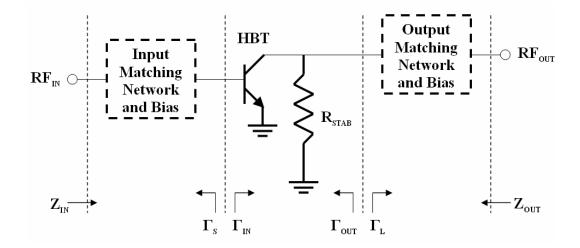

*Abstract* — This paper presents a 3.3V, 0.5µm pHEMT on 100µm gallium arsenside (GaAs) power amplifier operating across the 5150-5875MHz frequency range. Using a two-stage single-ended configuration with on-chip input/output matching networks, the designed amplifier provides a power gain of 20dB in conjunction with a 1dB compression level of -9dBm. A reverse isolation of greater than 30dB and DC power consumption of less than 43mW were achieved. A feedback resistor is utilized to eliminate potential stability problems in addition to a large capacitor on the bias voltages. The ideal elements are replaced with the foundry library elements and a layout is generated in preparation for fabrication. A test plan is detailed for measuring the design for comparison to the simulated performance.

Keywords --- MMIC, Power Amplifier, Single-Ended

## 1. <u>INTRODUCTION</u>

Modern RF and microwave transmitter designs utilize integrated circuit (IC) power amplifiers (PA) that directly interface to the radiating element of an antenna to provide maximum RF power output and efficiency. The goal of this PA design is efficiency – to get the most RF output power for a given DC power consumption. Utilization of a single voltage supply, such as a 3.3V coin cell battery, is required. The specifications for the PA design are as follows:

- (i) On chip drain and gate bias network

- (ii) On chip input and output matching networks

- (iii) FET size tuned for efficient power operation with good input & output VSWR

- (iv) Frequency: 5150 to 5875 MHz

- (v) Bandwidth: > 800MHz

- (vi) Gain, small signal: > 20dB

- (vii) Gain ripple: ±1 dB goal

- (viii) Output power: TBD @ 20-25% PAE (Power Added Efficiency)

- (ix) Supply voltage: +3.3V only, goal (3.0 to 3.6V range)

- (x) VSWR,  $50\Omega$ : < 1.5:1 input & output

- (xi) Size: 60 x 60 mil ANACHIP

This paper details the design of a C-band, two-stage singled-ended configuration PA fabricated in TriQuint TQPED GaAs process centered at 5.5GHz. This design exhibits a gain of 20dB, an input and output VSWR of less than 1.25:1, a reverse isolation greater than 30dB, a 1dB compression ( $P_{1dB}$ ) of -9dBm, and requires less than 43mW of DC power, all packaged within less than a 60mil x 60mil footprint.

#### 2. <u>DESIGN APPROACH</u>

Several topologies exist for PA circuits, with the single-ended topology being one of them. In a single-ended design, the RF input signal is applied to the gate while the amplifier RF output signal is extracted from the drain. Any stabilizing resistors must be implemented on the input of the transistor so the power loss across the resistors does not decrease the amount of output power. An ideal PA would have a high compression point, high efficiency, and high gain. Maximum output power occurs when the input impedance of the output matching network equals the conjugate match of the drain impedance for a specified Cripps impedance value.

To increase the gain of a single-stage amplifier, a second transistor can be configured in cascade. With the addition of another active component, comes additional gain and power consumption. It is important to optimize the driver amplifier stage for high efficiency so the overall PA efficiency remains high.

## 3. <u>SIMULATION SOFTWARE PACKAGE AND FOUNDRY</u>

## 3.1 SIMULATION SOFTWARE PACKAGE

Applied Wave Research, Inc (AWR) Design Environment Version 8.02 was used as the simulation software package for this project. The AWR Design Environment (AWRDE) suite is comprised of several software packages, including Analog Office (AO), which was utilized for the MMIC design of the PA. Linear and nonlinear circuit simulations were used to analyze the performance of the PA, while the tuning and optimization capabilities were exploited to finalize the design. Elements in the TQPED process library from TriQuint Semiconductor were used to create a final design that accounts for parasitics in the non-ideal components.

## 3.2 FOUNDRY

TriQuint Semiconductor is an independent semiconductor wafer foundry with capabilities of MMIC wafer processing. The TriQuint TQPED 0.5µm pHEMT process is ideal for switches, low-noise amplifiers, power amplifiers, and integrated transceivers. This particular process has D-mode and E-mode transistors, metal-insulator-metal (MIM) capacitors, spiral inductors, thin film resistors, and three metal interconnect layers. Using proprietary libraries developed by TriQuint Semiconductor that model the TQPED process and are compatible with AWRDE, more realistic simulations were performed and analyzed in the development of the PA.

## 4. <u>DESIGN AND CIRCUIT SIMULATIONS</u>

This section details the design of the PA, starting with the transistor model supplied by TriQuint based on the TQPED process, followed by the stabilization circuitry, transistor biasing, and matching network (input and output) designs.

#### 4.1 TRANSISTOR DEVICE – BIAS POINT AND CRIPPS ANALYSIS

The active element used in this amplifier design is an E-mode pHEMT transistor. This particular transistor is a commercially available GaAs process from TriQuint Semiconductor. The exact transistor model used in the TQPED 1.1.21 library was the TQPED\_EHSS\_T3, which is an adjustable-length 0.5µm transistor. A width of 15µm and a gate finger value of four were chosen for this design. Table 1 lists the parameters of the utilized transistor.

| Description                 | Properties    |

|-----------------------------|---------------|

| pHEMT Model Type            | TQPED_EHSS_T3 |

| Gate Width (W)              | 15µm          |

| Number of Gate Fingers (NG) | 4             |

Table 1. pHEMT E-Mode Transistor Properties

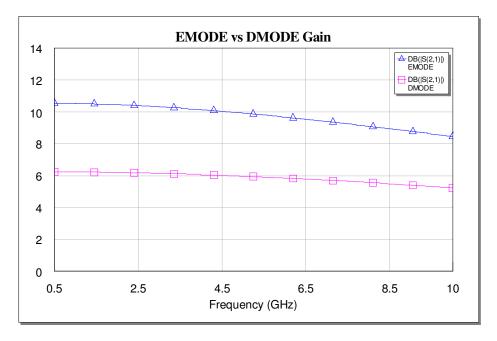

Prior to selecting the E-mode device, a comparison between the D-mode and E-mode was performed. The E-mode transistor has a higher gain for a given DC power consumption compared to the D-mode, as shown in Figure 1.

Figure 1. D-mode vs E-mode Achievable Gain

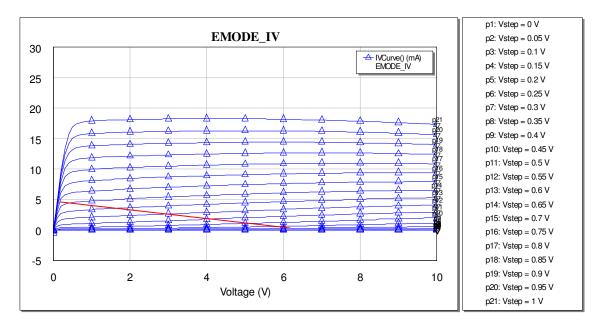

Using a swept voltage generator on the gate and drain, the IV curves for E-mode transistor is generated and illustrated in Figure 2.

Figure 2. IV Curves for the E-mode (4x15um) pHEMT

From the IV curves, it was determined that the optimum bias point voltage for a  $V_{DS}$  of 3.3V is  $V_{GS}$  equal to 0.75V. This bias value can be obtained with a resistive divider network using the single 3.3V supply.

A Cripps Method load-line analysis is a technique that can be used to determine the optimum output impedance needed to be present at the output stage of the PA. Using the load-line shown in Figure 2, the usable region of both the drain current and drain-to-source voltage is used to derive the performance of the PA as:

$$\begin{split} V_{GS} &= 0.75V \\ V_{DS} &= 3.3V \\ V_{DSmin} &= 0.6V \\ V_{DSmax} &= V_{DS} + (V_{DS} - V_{DSmin}) = 3.3V + (3.3V - 0.6V) = 6.0V \\ IDSS &= 8.7mA \\ I_{DSmax} &= 17.4mA \end{split}$$

The RF output power of the PA should be approximately equal to  $(\Delta V_{DS} \times \Delta I_{DS})/8 \approx 11.7$ mW. With the device consumption at approximately 29mW, the Power Added Efficiency (PAE) should be approximately 40%. However, the final PA design will have a lower PAE value since the design will be a dual-stage configuration and the power loss in the resistive biasing networks.

The Cripps resistance is calculated from the load-line analysis as  $\Delta V_{DS} / \Delta I_{DS}$  resulting in a value of 310 $\Omega$ .

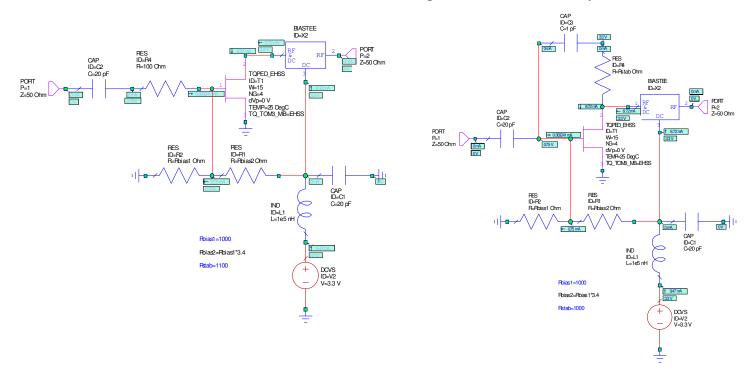

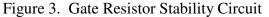

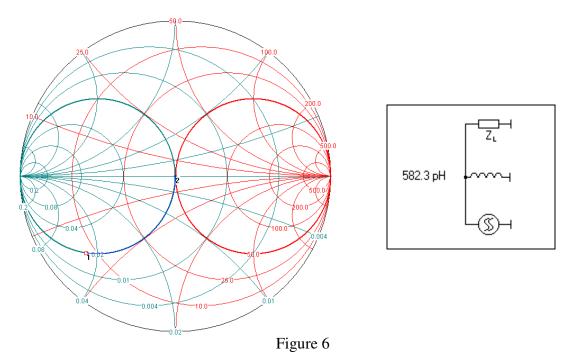

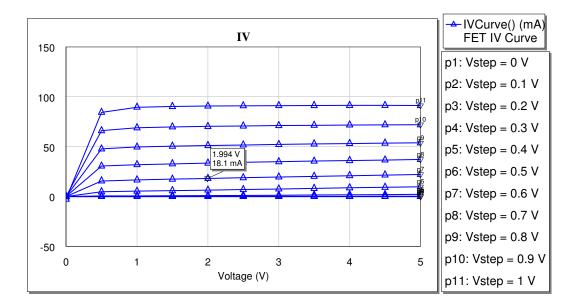

#### 4.2 BIAS CIRCUITRY AND STABILITY

Stability is one of the most critical properties of an amplifier circuit. An unstable circuit will oscillate and hence not perform as a controlled amplifier. Likewise, a main goal of the design is to use a single supply voltage, such as a coin cell battery. Therefore, a resistive divider network is necessary to achieve the gate bias (0.75V) while the coin cell battery voltage of 3.3V will directly supply the drain bias. It was determined early in the modeling phase that the resistor values of the gate bias network directly affect the stability of the design. To combat this effect, two separate stability circuits were studied and compared. A series gate resistor, shown in Figure 3, was compared against a feedback resistor, shown in Figure 4. Since a main goal of the PA design is to minimize power consumption and maximize PAE, a DC blocking capacitor was added in series with the feedback resistor to eliminate power loss in this stability circuit.

Figure 4. Feedback Stability Circuit

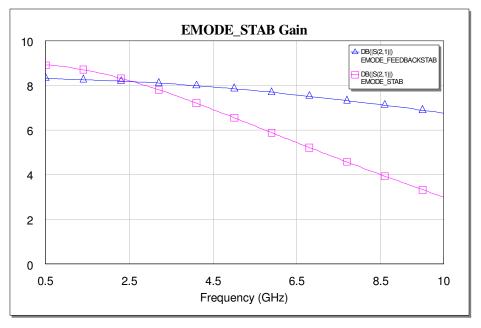

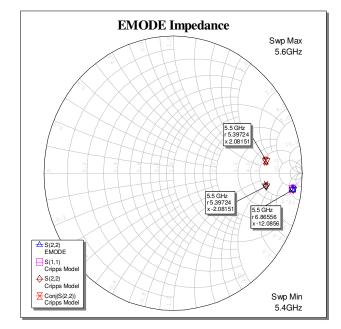

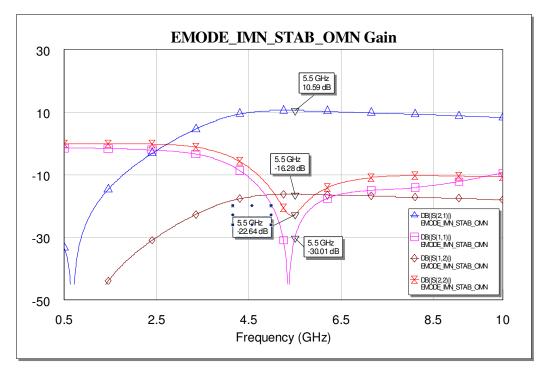

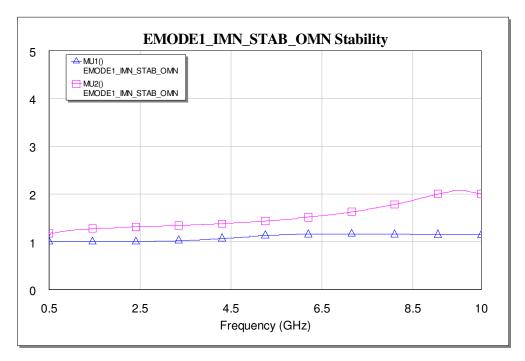

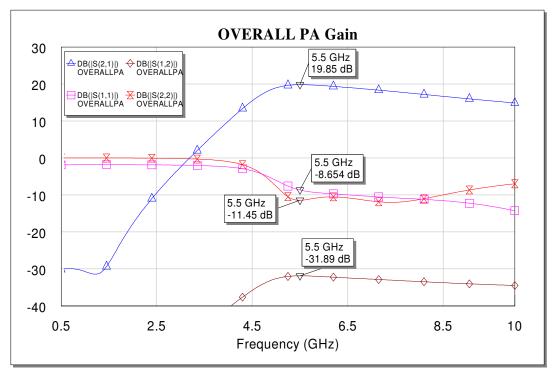

The performances of both circuits are shown in Figures 5 and 6. The stability, Figure 5, is slightly better across the 0.5-10GHz frequency range for the feedback resistor circuit (pink and blue curves). However the real advantage of the feedback stability circuit is noticed in comparing the gain, shown in Figure 6. The achievable gain rolls off much faster using the gate series stability circuits (pink curve) compared to the feedback stability circuits (blue curve). Thus the feedback stability circuit was chosen for the PA design.

Figure 5. Stability for the Series Gate Resistor Circuit and the Feedback Resistor Circuit

Figure 6. Gain for the Series Gate Resistor Circuit and the Feedback Resistor Circuit

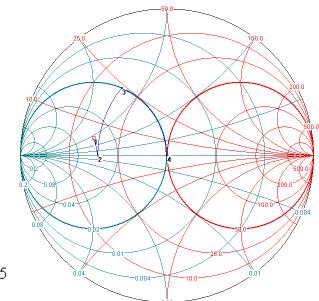

## 4.3 INPUT AND OUTPUT MATCHING NETWORKS

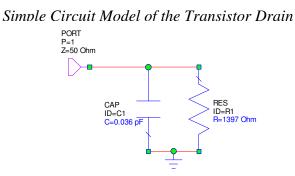

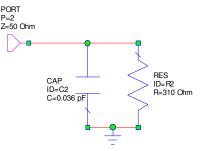

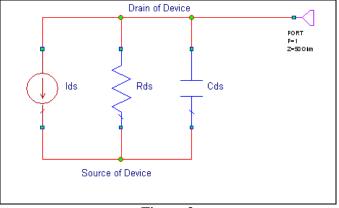

The output impedance of the E-mode transistor at the center frequency of the design is shown on the smith chart in Figure 7. Using a simple circuit to model the drain impedance of the E-mode, the shunt capacitance and resistance were chosen so the impedance of the circuit was

equal to the output impedance of the transistor. Once the capacitance and resistance values are known, the resistance is changed to the Rcripps value, and this new impedance is used to design the PA. For maximum power transfer, the output matching network (OMN) of the PA is designed to supply the complex conjugate of the Rcripps model. Figure 8 illustrates the OMN design, which consists of shunt inductance of 3.4nH and a series capacitance of 251.5pF.

Simple Circuit Model of the Transistor Drain with Rcripps

Figure 7. Transistor Library Model and Rcripps Circuit Model Output Impedance

Figure 8. Output Matching Network Design

The input matching network (IMN) is designed to match input impedance of the transistor to  $50\Omega$ . A series inductance of 1.52nH comprises the IMN. A large capacitor is included in series to act as a DC blocking capacitor while minimizing its affect on the impedance matching. Figure 9 illustrates the single-stage PA design using ideal components. The linear S-parameter performance of the ideal single-stage PA design is shown in Figure 10 and the overall stability is shown in Figure 11.

Figure 9. Ideal Single-Stage PA Design

Figure 10. S-Parameter Performance of Ideal Single-Stage PA Design

Figure 11. Stability Performance of Ideal Single-Stage PA Design

#### 4.4 DRIVER AMPLIFIER

The driver amplifier is used to provide additional gain but with minimal DC power consumption. In addition, the driver amplifier must still be linear in the region where the output-stage amplifier design is in compression. The bias point of the driver amplifier is based on taking approximately 20% of IDSS of the output-stage (reference Figure 2).

Using the load line shown in Figure 12, the RF output power of the driver stage amplifier is approximately  $(\Delta V_{DS} \times \Delta I_{DS})/8 \approx (2(3.3V - 0.33V) \times 5mA)/8 \approx 3.7mW$ . With the device consumption at approximately 8.25mW, the Power Added Efficiency (PAE) should be approximately 45%. However it is expected that the actual PAE will be lower due to the additional power loss in the biasing network.

Figure 12. IV Curves for E-mode Driver Amplifier

The driver amplifier stage is designed using the same steps described in sections 4.2 and 4.3. The final ideal driver amplifier stage design is shown in Figure 13 with its linear S-parameter performance and stability shown in Figures 14 and 15, respectively.

Figure 13. Ideal Driver Amplifier Design

Figure 14. S-Parameter Performance of Ideal Driver Amplifier Design

Figure 15. Stability Performance of Ideal Driver Amplifier Design

#### 4.5 TWO-STAGE SINGLE-ENDED PA DESIGN

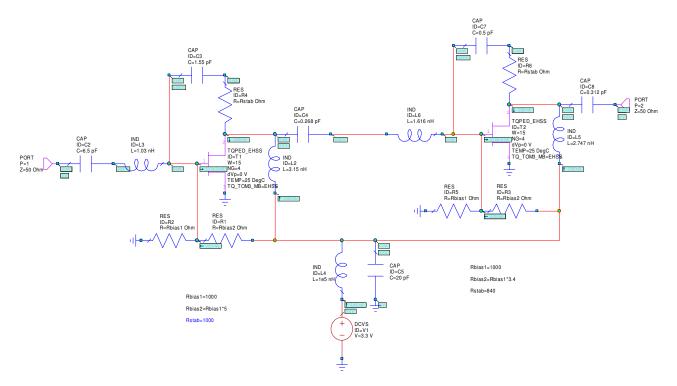

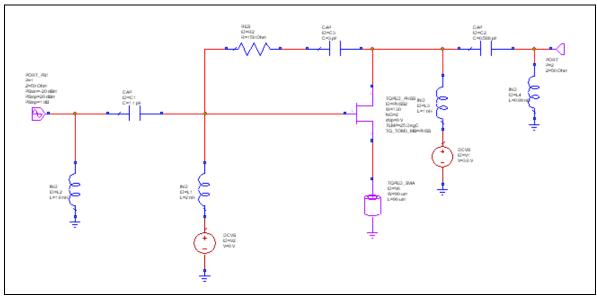

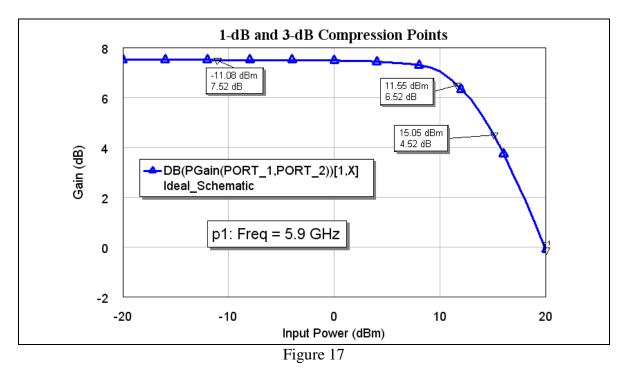

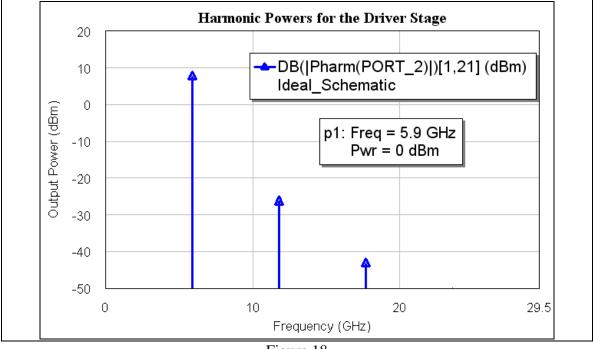

The final PA design consists of an input driver amplifier stage followed by an output power amplifier stage. The output of the driver amplifier stage needs to be matched to the input of the power amplifier stage. Figure 16 shows the final PA design using ideal components, with Figure 17 illustrating the linear S-parameter performance and Figure 18 illustrating the overall stability.

Figure 16. Ideal Two-Stage Single-Ended PA Design

Figure 17. S-Parameters Performance of Ideal Two-Stage Single-Ended PA Design

Figure 18. Stability Performance of Ideal Two-Stage Single-Ended PA Design

#### 5. <u>LAYOUT AND FINAL SIMULATED PERFORMANCE</u>

#### 5.1 IDEAL VERSUS NON-IDEAL COMPONENTS

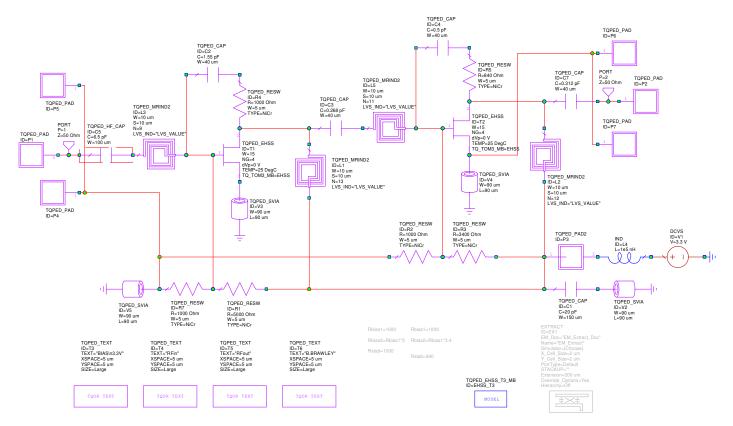

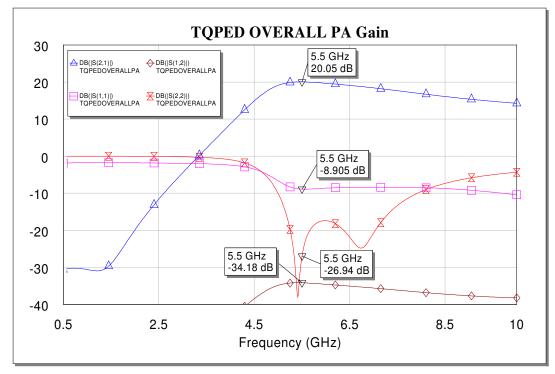

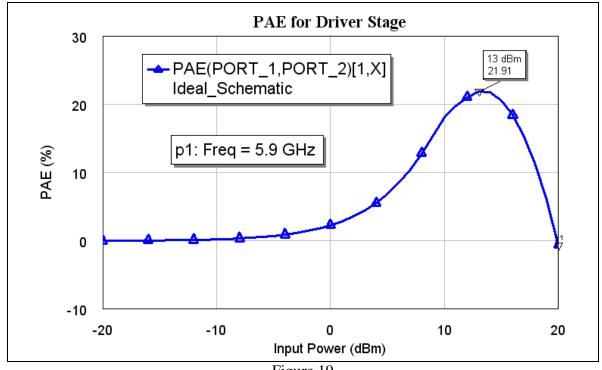

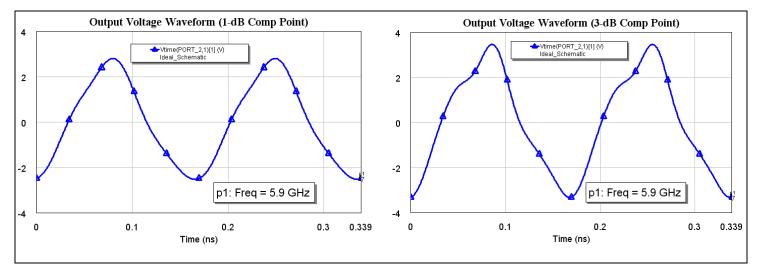

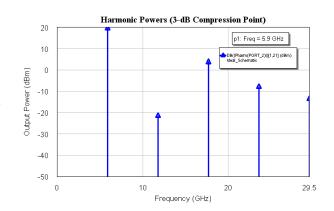

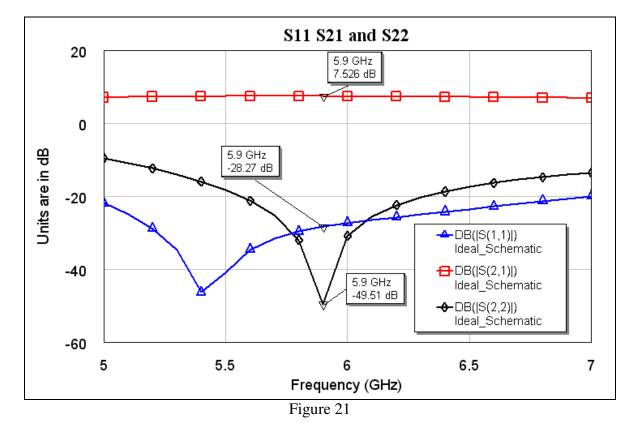

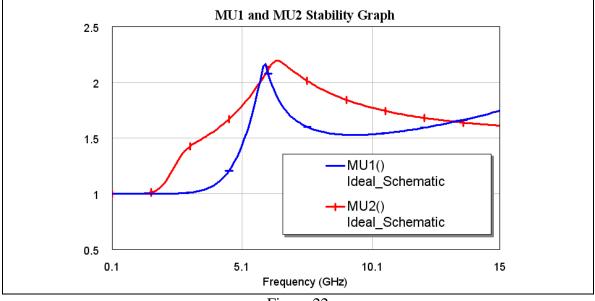

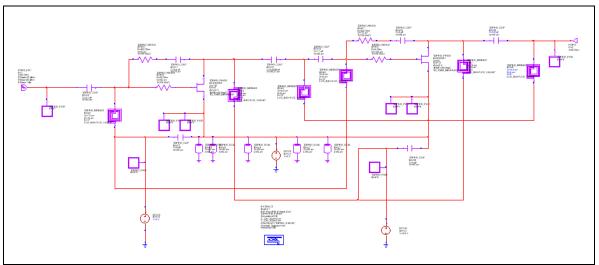

Like the transistors, all the ideal components can be replaced with TriQuint TQPED Library components. These components model the non-ideal parasitics that arise in all real components. Replacing these components one at a time, while tuning and optimizing the circuit in discrete stages allows for a better design. In addition, since the components on the output of the transistor stages will have small resistance values associated with them, the output power will be reduced. Also, on-chip inductors and capacitors have lower quality factors (Q) resulting in less optimum performance. Figure 19 illustrates the non-ideal PA design with all ideal components replaced with TQPED Library components, including RF and Bias pads. Figures 20 and 21, respectively, show the S-parameter and stability performance with these non-ideal components, while Figure 22 shows the 1dB compression for the design frequency. Figure 23 shows the PAE of the final non-ideal design.

Figure 19. PA Design with Non-Ideal Components

Figure 20. S-parameter Performance of PA Design with Non-Ideal Components

Figure 21. Stability Performance for PA Design with Non-Ideal Components

Figure 22. Power 1dB Compression for PA Design with Non-Ideal Components

Figure 23. PAE for PA Design with Non-Ideal Components

Table 2 lists a comparison between the PA performance with the ideal and non-ideal components. Notice the slight degradation in performance due to the added resistance and lower Q factors of the components.

| Parameter                            | Ideal Circuit | Non-Ideal Circuit |

|--------------------------------------|---------------|-------------------|

|                                      | Performance   | Performance       |

| Frequency [f]                        | 5.5GHz        | 5.5GHz            |

| Gain [S <sub>21</sub> ]              | 19.9          | 20.0              |

| Input Match [S <sub>11</sub> ]       | -8.7          | -8.9              |

| Output Match [S <sub>22</sub> ]      | -11.5         | -26.9             |

| Reverse Isolation [S <sub>12</sub> ] | -31.9         | -34.2             |

| DC Power                             | 42.3mW        | 42.7mW            |

Table 2. Comparison Between Ideal and Non-Ideal Components Performance

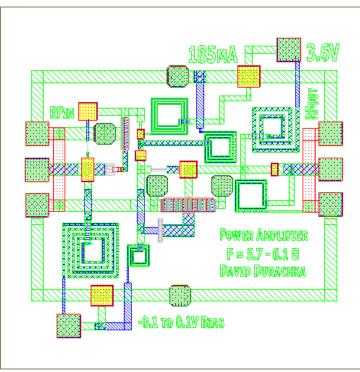

## 5.2 LAYOUT

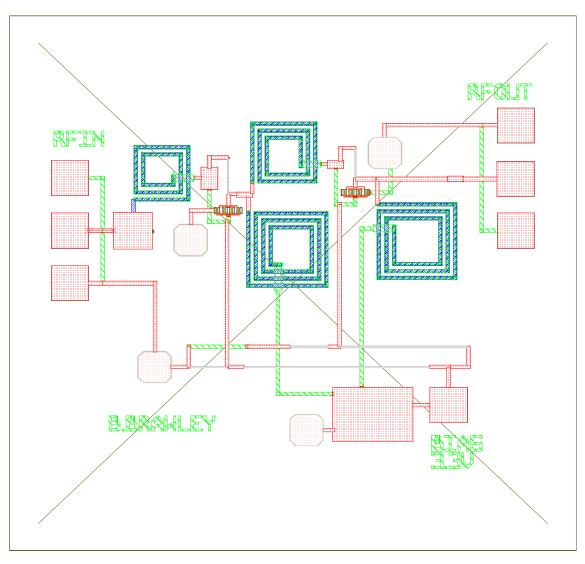

Once the ideal components are replaced with the non-ideal components, a layout can be generated. The TriQuint TQPED process has 3 metal layers with different thickness values. In preparation for bench testing of the fabricated PA, a ground-signal-ground pad configuration is incorporated, with the pads on a 120 $\mu$ m pitch. Figure 24 illustrates the generated layout in 2D, while figure 25 depicts the layout in 3D.

Figure 24. Final PA Design Layout

Figure 25. 3D Image of Final PA Design Layout

## 5.3 EXTRACTION OF LAYOUT MODEL

Once the layout is generated and signal, power, and ground paths are included, the trace runs can be extracted and included in the non-ideal simulation. Additional degradation in performance is incurred with the addition of these extracted traces.

## 5.4 FINAL DESIGN PERFORMANCE

Overall, the designed PA exhibits moderate output power, moderate efficiency, high gain, high reverse isolation, and low DC power consumption all encompassed in a compact layout. Table 3 lists the properties and performance of the designed PA.

| Parameter                            | Simulated Performance |

|--------------------------------------|-----------------------|

| Center Frequency $[f]$               | 5.5GHz                |

| Bandwidth                            | 13%                   |

| Gain [S <sub>21</sub> ]              | 20dB                  |

| Gain Ripple                          | ±0.5dB                |

| Input Match [S <sub>11</sub> ]       | -9dB                  |

| Output Match [S <sub>22</sub> ]      | -27dB                 |

| Reverse Isolation [S <sub>12</sub> ] | -34dB                 |

| 1dB Compression                      | -9dBm                 |

| DC Power                             | 12mW                  |

| PAE                                  | 20%                   |

| Layout Footprint                     | 60mil x 60mil         |

Table 3. Simulated Performance of the Designed PA

#### 6. **DISCUSSION AND FUTURE WORK**

#### 6.1 **DISCUSSION**

Overall, the PA design has moderate performance and all simulations indicate that the design will perform close to the design specifications. However there are some areas for improvement. First, the driver amplifier stage could be designed to operate with less power consumption, either by using a lower bias voltage or by using a smaller sized transistor. In addition, the inter-stage matching network should be designed for a power match instead of a  $50\Omega$  match. This would have increased efficiency while still maintaining the necessary gain requirements.

#### 6.2 FUTURE WORK

In order to verify the performance of the designed PA presented, the circuit must be fabricated and measured. A comparison of measured performance to the simulated performance allows for validation of the models used in the design. The following test plan will be utilized to test the PA upon the completion of its fabrication.

#### 6.2.1 Test Plan

#### Test Equipment

The following is a list of the required test equipment to measure both the linear parameters and the power performance of the PA:

| Power Supply     | Network Analyzer  | Wafer Probe Station |

|------------------|-------------------|---------------------|

| Signal Generator | Spectrum Analyzer | Low-loss RF cables  |

#### Linear Parameter Measurements

The following steps are used to measure the linear (S) parameters of the PA:

- (1) Calibrate the network analyzer across the 0.5GHz to 10GHz frequency range using proper calibration standards (short, open, load, thru – SOLT). Include all RF cables necessary to connect the network analyzer to the probe station in the calibration.

- (2) Turn on DC power supply and set voltage to 0V.

- (3) Turn off DC power supply.

- (4) Place the DC bias probe on the pad of the chip labeled "+3.3V".

- (5) Place the input RF probe (ground, signal, ground) on the pad of the chip labeled "RFin".

- (6) Place the output RF probe (ground, signal, ground) on the pad of the chip labeled "RFout".

- (7) Turn on the DC power supply and slowly adjust the voltage to +3.3V while watching the current draw (simulated current consumption is < ?mA)

- (8) Record the S-parameter data (S11, S21, S12, and S22).

## Power Measurements

The following steps are used to measure the power peformance of the PA:

- (1) Calibrate the insertion loss in the RF cable used to connect the signal generator to the probe station and the RF cable used to connect the spectrum analyzer to probe station.

- (2) Turn on the DC power supply and set the voltage to 0V.

- (3) Turn off the DC power supply.

- (4) Place the DC bias probe on the pad of the chip labeled "+3.3V".

- (5) Place the signal generator probe (ground, signal, ground) on the pad of the chip labeled "RFin".

- (6) Place the spectrum analyzer probe (ground, signal, ground) on the pad of the chip labeled "RFout".

- (7) Turn on the DC power supply and slowly adjust the voltage to +3.3V while watching the current draw (simulated current consumption is < ?mA)

- (8) For Pin vs Pout measurement, set the signal generator to the frequency of interest (?) and sweep the power up to but not exceeding 0dBm and record the output power values from the spectrum analyzer.

- (9) For harmonics analysis measurements, set the signal generator to a center frequency of 5.5GHz and sweep the spectrum analyzer across a broad frequency range and record harmonic content power levels.

## ACKNOWLEDGMENT

The author is indebted to Applied Wave Research, Inc (AWR) for the use of Analog Office design software package and Triquint Semiconductor for the use of their design libraries and for the future fabrication of the designed circuit.

Minhaj Raza EE 787 WIDE BAND LOW NOISE AMPLIFIER 1.2-3GHz Dec 9<sup>th</sup> 2008

#### Abstract:

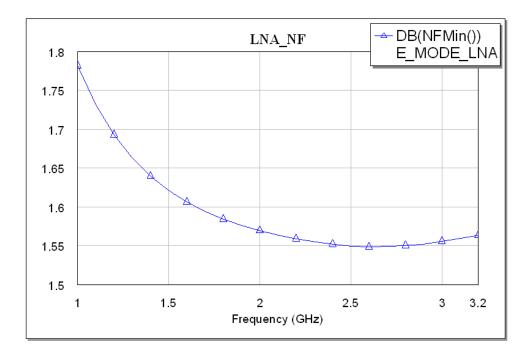

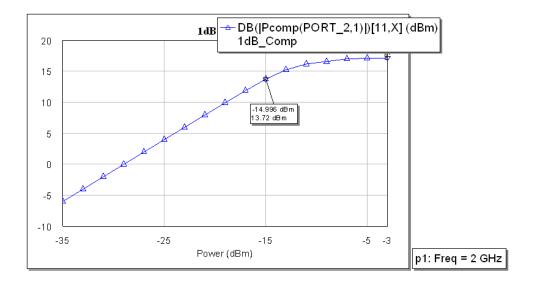

The design of a Monolithic Microwave Integrated Circuit (MMIC) low power low noise amplifier (LNA) circuit will be described in this paper. The use of LNA Design is applicable in the industrial fields of GPS, Medical, and Cellular technologies. The amplifier operates with 3 VDC supply voltage at VDD and a 0.75 VDC at VGG and total current draw of 76 mA. The amplifier has a 1 dB bandwidth of more than 1.8 GHz (1.2 GHz-3 GHz). The amplifier has the NF of less 1.7 db throughout its working frequency. The amplifier achieves a power gain of 29 dB with the input 1 dB compression point of -14.5 dBm. The amplifier has the input port match (S11) of -14dB or better, and in addition the output port match (S22) is also -13 dB or better. The unconditional stability of the LNA is also observed for the entire working frequency.

#### Introduction:

This report will focus on the design, simulation, layout, optimization and test plan for the low power low noise amplifier. The normal use of a LNA is at the front end of the RF receiver system providing the first stage of amplification after the receive antenna and adding as little noise as possible with providing the maximum gain. Large gain in the first stage of the receiving chain also factors into setting the overall noise figure of the receiver; however, a high gain and low noise figure amplifier is difficult to obtain using a single-stage design. Therefore, multi-stage designs are utilized to incorporate both of these desired traits.

#### Design Approach:

The design consists of a two-stage amplifier design powered by a positive 3VDC source for drain ports of the PHEMT and another 0.75 VDC source for the gate ports of the PHEMT. Two 6 X 50um EMODE FET's are used in the amplifier due to their higher gain and lower noise figure. A feedback resistor in series with a capacitor was used to flatten the output response of the LNA as shown in Figure 1.

Figure 1. PHEMT with feedback Resistor

The simplest form of the design (common-source) was used to approach the design goals. In it, the RF input signal is applied to the gate of the PHEMT while amplifier RF output signal is extracted from the drain port. The input and output matching networks perform impedance transformations to provide noise and power matching, respectively. The goal is to have low noise and high gain characteristics at the same time. Maximum output power occurs when the input impedance equals the conjugate match of the source impedance, resulting in  $\Gamma in =$  $\Gamma s^*$ . The condition for minimal noise is met when  $\Gamma s = \Gamma opt$ . An input matching network (IMN) is designed to impedance match  $\Gamma opt$  of the transistor to 50 $\Omega$ ,  $\Gamma opt$  is the the optimum reflection coefficient or the lowest noise figure at a designed frequency (2GHz). This information was obtained from the .s2p data file of the measured data provided in the class. Figure 2 shows a generalize input and output matching circuit of an amplifier except for a series resistor added prior to the output matching network.

Figure 2. Input and Output Matching

The stability of the circuit was observed at this point, and it was noticed that a stabilizing circuit network was required to add stability resistors to stabilize the the LNA for the entire working frequency. Figure 3 shows a output stability circuit.

Figure 3. Output Stability Resistor Network

To achieve a high gain LNA, a two-stage design is employed. This architecture allows for the first stage to be designed with an extremely low noise figure, hence setting the overall noise figure of the LNA. Then the second stage provides the necessary amplification to achieve an overall high gain.

#### SIMULATION SOFTWARE

Applied Wave Research (AWR) Microwave Office provided by the Applied Wave Research version 9.01 Build 4229 rev1 (58736), was used as the simulation software package for this project. Linear and nonlinear circuit simulations were used to analyze the performance of the LNA. Elements in the TQPED process library TQOR\_TQPED v1.1.21 from TriQuint Semiconductor were used to create a final design that accounts for parasitics in these non-ideal components. The initial design was generated using the lumped elements and gradually these lumped elements were replaced by TriQuint parts.

#### BIASING

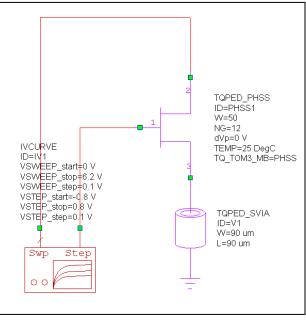

The first step in the design process is to determine the DC operating point. This is accomplished by sweeping the drain voltage (VDS) and the gain voltage (VGS) of the transistor. The EMODE pHEMT is used in calculating the DC IV curves, shown in Figure 4 It is determined that an appropriate bias for the LNA is:

Figure 4. IV Curve Circuit

Figure 5. IV Curve for the PHEMT

Note that the biasing gate voltage is positive because the pHEMT is an EMODE.

#### STABILITY

The next step in the design process is to stabilize the transistor. Because the LNA is being designed for a minimum NF, the stabilizing network should be placed on the output side of the LNA. Two methods of stabilizing the transistor were studied, (1) a feed back resistor between the drain and gate, and (2) a shunt resistor and a series resistor on the drain. Both of these options were attempted separately, but neither provided unconditional stability. However, when used in conjunction with one another, the LNA became unconditionally stable from 1 GHz to 3.2 Ghz.

Since the LNA is being designed to operate via a battery, it is essential to minimize wasted power loss in any portion of the stabilizing network. Therefore, DC blocking capacitors were used in series with the stabilizing resistors to minimize the amount of power dissipated by the resistors. DC blocking capacitors are also utilized to isolate the inter-stages of the amplifier in addition to the external RF ports on the amplifier from the various bias voltages.

#### INPUT AND OUTPUT MATCHING NETWORK

Subsequently the input matching network was designed for the best possible noise figure and the output matching network was designed for maximum gain as well as the best input and output match. Both networks are comprised of series capacitors and shunt inductors. It should be noted that all components are ideal in this initial design phase, including the components used in the previously discussed stabilizing network.

#### IDEAL SINGLE-STAGE DESIGN

After designing the input and output matching networks, a single-stage design is complete. Favorable results were obtained after simulating the design:

Gain = 15 dB NF = 1.5 dB Match (input) = -15 dB. Match (output) = -20 dB

#### IDEAL TWO-STAGE DESIGN

After the ideal single stage design yielded promising results, two identical single stages were cascaded together. The ideal cascaded system provided the following performance:

Gain = 29.2 dB NF = 1.65 dB Match (input) = -13 dB Match (output) = -22dB

Final Design:

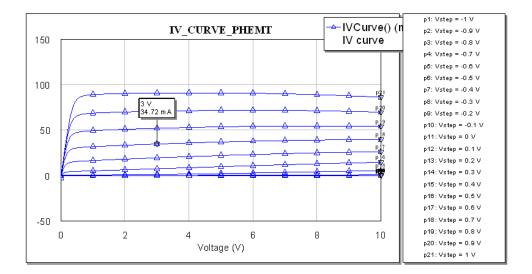

Figure 6. Complete Circuit Design of the LNA with TriQuint Parts

Figure 7. Linear / S-Parameters of LNA

It was observed that by comparison the E-mode PHEMT has better gain response with a low Noise Figure than the D-mode.

Figure 8. Noise Figure Response of the PHEMT

Figure 9.1 dB compression point for the LNA

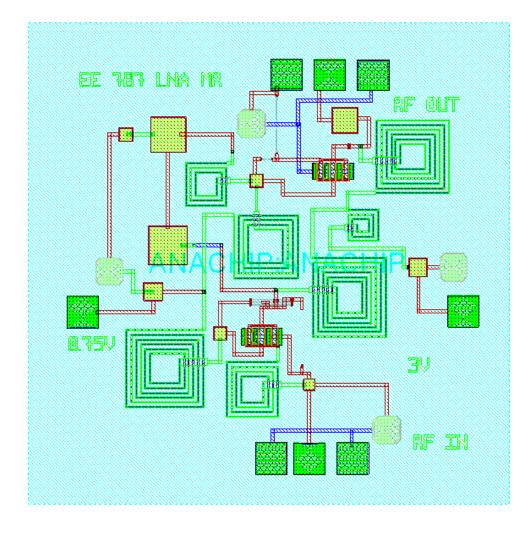

Figure 10. Final Layout of the LNA

#### TEST PLAN

There are three measurements of interest for the LNA: (1) S-parameter measurements, (2) noise figure measurements, and (3) compression measurements.

First, power must be applied to the chip. To do this, apply a needle probe to the voltage supply to 0.75 and 3 volts pads on the chip. Slowly, increase the voltage to 3 VDC with also providing 0.75 VGS and verify that the power supply is drawing approximately 36 and 45 mA of current for both stages.

For the s-parameter measurements, first calibrate the network analyzer. Then, connect the GSG probes to the RF IN pad and the RF OUT pad on the chip.

Finally measure the parameters on the network analyzer and save the data to a disk. A similar setup is employed when taking the noise figure measurements. First calibrate the noise figure meter. Apply a noise source at the RF IN side of the chip. Take a measurement at the RF OUT side of the chip and save the data.

A signal generator in conjunction with a spectrum analyzer is used to make the compression measurements. Connect the signal generator to the RF IN side of the chip. Connect the spectrum analyzer to the RF OUT side of the chip. Set the signal generator to 2.4 GHz. Start at -40 dBm, and sweep the input power in 1dBm increments until compression is reached. Save the data to a disk.

#### SUMMARY

Overall, the designed LNA exhibits low noise figure, high gain, high reverse isolation, and nominal DC power consumption all encompassed in a compact layout. A comparison of measured results to the simulated performance will allow for validation of the models used in the design.

# Abstract

This paper describes the design and simulation of a two stage broadband small signal amplifier using the TriQuint process for MMIC fabrication. The design uses two E-Mode pHEMT devices with feedback to achieve a gain of  $23 \pm 1$  dB from 2.305 GHz to 5.785 GHz. The total DC power consumption is 19.68 mW from two 1.5 V supplies. All simulations were performed in Microwave Office version 8.01r build 4229 from Applied Wave Research, Inc. (AWR) with the TriQuint process library version 1.1.21.

# Introduction

This broadband small signal amplifier is designed for low power and small size. It can be operated off of two 1.5 volt batteries drawing 6.56 mA each. It fits within a 30 x 60 mil area including scribe lines. Each stage is identical with the same size FET and voltage divider bias network. The frequency of operation is from 2305 MHz to 5875 MHz.

The front end of the amplifier consists of a low pass filter with a cutoff frequency of about 5.8 GHz. Next is the input matching network followed by the first stage FET. An interstage matching network sits between the two stages and at the end is the output matching network (Figure 1).

Figure 1 Block diagram of 2-stage broadband amplifier

# **Design Approach**

The specifications and achieved goals for this design are shown below (Table 1). All but one of the specifications have been achieved and the power and size have been cut in half. The output IP3 was not meet due to an oversight in the requirements that went unnoticed until the design had been completed.

| Parameter           | Specification          | Goals                  |

|---------------------|------------------------|------------------------|

| Frequency           | 2305 to 5875 MHz       | 2305 to 5875 MHz       |

| Bandwidth           | >3575 MHz              | >3575 MHz              |

| Gain (small signal) | ≥ 20 dB                | 22 dB                  |

| Gain Ripple         | ± 1dB                  | ± 1dB                  |

| Output IP3          | >+20 dBm               | +6.9 dBm               |

| VSWR, 50 Ω          | < 1.5:1 input & output | < 1.5:1 input & output |

| Supply voltage      | + 3.3 V                | + 1.5 V                |

| Size                | 60 x 60 mil ANACHIP    | 30 x 60 mil            |

| FET size            | 4x15                   | 4x15                   |

Table 1 Design specifications and achieved goals.

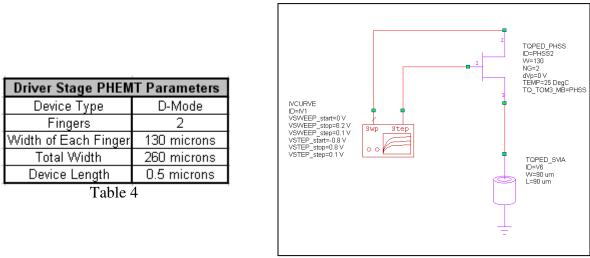

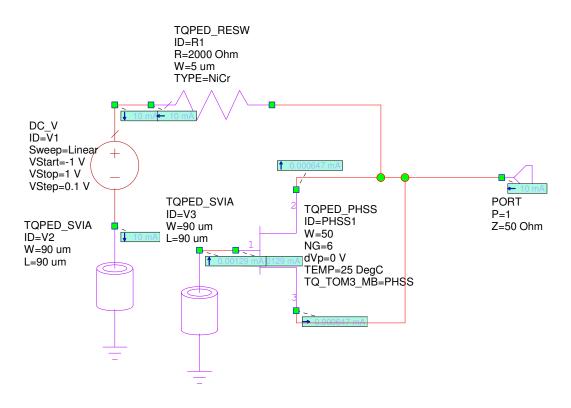

The first step of this design is to determine the type of FET to use. The Emode PHEMPT provides higher gain than the Dmode at the same power with less noise. The Emode is also biased with a positive gate voltage, which will make the bias network design simpler. With the type and size of the device known, an IV curve trace is generated to determine the bias voltage (Figure 2).

Figure 2 IV curve for 4x15 Emode PHEMPT

Keeping low power in mind, we would like to be less than 10 mW DC power for each stage. With a 1.5 V supply, we have a budget of 6.67 mA. This translates to VGS = 0.7V.

The bias network is a simple voltage divider with 2000  $\Omega$  and 1750  $\Omega$  resistors (Figure 3). An 8  $\Omega$  gate resistor was added for stability. A large inductor is used to isolate the rf signal from the DC source, and a capacitor to ground is also used to short out any rf that makes it past the inductor. The voltage divider network also provides a shunt feedback path on each stage. The feedback path helps increase bandwidth and stability. Another design approach to increase bandwidth is a distributed design, but that would require more components and more power. Since this design focuses on low power and small size, the feedback amplifier design is used.

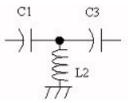

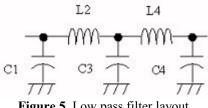

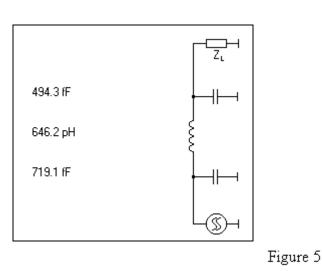

The input, interstage, and output matching networks all use a tee network layout with two capacitors and one inductor (Figure 4). Early simulations looked promising, but the gain did not fall off at high frequencies. A 5-element low pass Pi network filter (Figure 5) was added at the input to cut off the high frequency gain. If a larger bandwidth is desired, the low pass network elements can be adjusted, but the gain will still slowly decrease as the frequency increases.

Figure 3 DC bias network with FET.

Figure 4 Matching network layout.

Figure 5 Low pass filter layout.

#### Simulations

The following results were simulated in Microwave Office version 8.01r build 4229 from Applied Wave Research, Inc. (AWR) with the TriQuint process library version 1.1.21. The FETs use the TOM3 model.

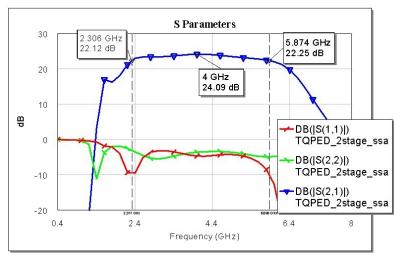

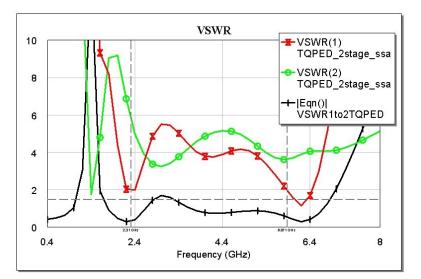

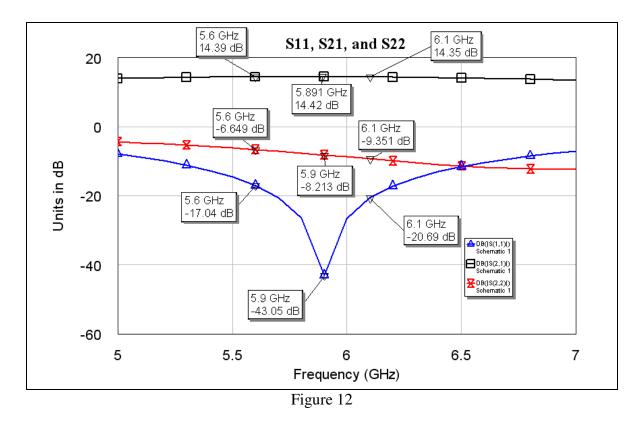

The gain and match are shown in figure 6. The median of the gain is 23.1dB with a ripple of  $\pm 1$ dB over the targeted frequency range. The minimum gain of 22.12 dB is at 2.305 GHz and the maximum gain of 24.09 dB at 4 GHz. The match could be better, but at the cost of gain flatness. The VSWR is shown in figure 7 and meets the specification of < 1.5:1 for the entire bandwidth expect for a small range around 3 GHz. This was noticed after the design had been frozen and went unnoticed because of not rechecking the VSWR after rerouting some traces in the layout.

Figure 6 Gain and match.

Figure 7 VSWR.

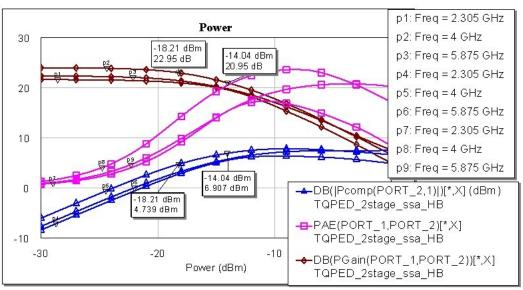

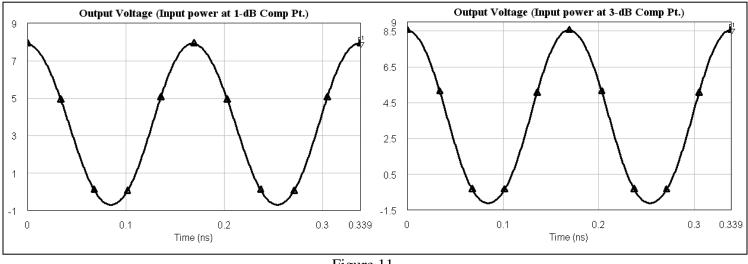

The output power at the 3dB compression point is 6.9 dBm (Figure 8). The output IP3 specification is > +20 dBm, but during the design, the power gain was mistakenly used as the check for this parameter. Increasing the DC power will increase the rf output power, but at the cost of efficiency, and this design may burn out at high DC power.

Figure 8 3dB power compression.

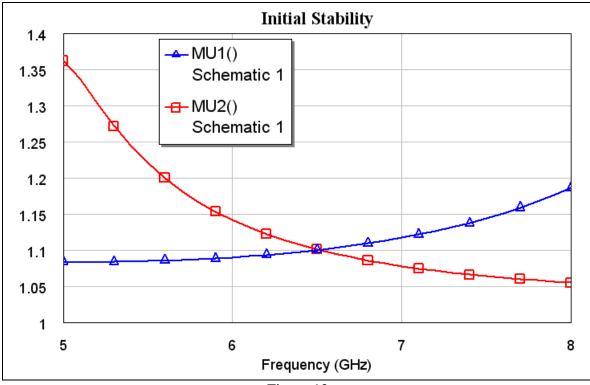

Figure 9 shows that the design is unconditionally stable for all frequencies.

Figure 9 Stability.

# Schematics

Figure 11 DC schematic.

# Layout

# Test Plan

After fabrication, the amplifier will be tested in lab and compared to the simulated results. The test equipment available includes the Agilent 8510 vector network analyzer, Cascade Model 43 wafer probe station with up to 4 RF probes and 4 DC needle probes, signal generators, and a spectrum analyzer. The steps to complete testing are the following:

## **S-Parameter Measurements**

- 1. Power up the equipment.

- 2. Calibrate the network analyzer using open, short, thru, and load test fixtures.

- 3. Mount circuit on probe station and connect probes RF in, RF out, and both DC sources.

- 4. Set each DC supply to 1.5 volts and limit each current to 10mA.

- 5. Measure the s-parameters from 100 MHz to 8 GHz and note S21 at 2.305 GHz, 4 GHz and 5.875 GHz (see table below).

- 6. Save the s2p file.

## **IP3** Measurements

- 1. Note the power losses in the cables.

- 2. Connect the signal generator to the input of the device.

- 3. Connect the spectrum analyzer to the output of the device.

- 4. Connect and set the DC bias as above.

- 5. Set the frequency to 2.305 GHz and sweep the input power from -30 dBm to -10 dBm noting the output power at 2 dB intervals (see table below).

- 6. Repeat step 5 at 4 GHz.

- 7. Repeat step 5 at 5.875 GHz.

|                 | Gain           |               |

|-----------------|----------------|---------------|

| Frequency (GHz) | Simulated (dB) | Measured (dB) |

| 2.305           | 22.12          |               |

| 4               | 24.09          |               |

| 5.875           | 22.25          |               |

| Cable loss at inp | ut               | Cable loss at output |                  |  |

|-------------------|------------------|----------------------|------------------|--|

|                   | Power            |                      |                  |  |

| Pin (dBm)         | Pout (2.305 GHz) | Pout (4 GHz)         | Pout (5.875 GHz) |  |

| -30               |                  |                      |                  |  |

| -28               |                  |                      |                  |  |

| -26               |                  |                      |                  |  |

| -24               |                  |                      |                  |  |

| -22               |                  |                      |                  |  |

| -20               |                  |                      |                  |  |

| -18               |                  |                      |                  |  |

| -16               |                  |                      |                  |  |

| -14               |                  |                      |                  |  |

| -12               |                  |                      |                  |  |

| -10               |                  |                      |                  |  |

# **Summary and Conclusions**

This design of a broadband small signal amplifier is both low power and very small. Some minor modifications can be made to better the match and VSWR while being careful not to affect the gain ripple. There were no noise data in the TOM3 model of this device, but noise parameters should be looked into if this design is used for low noise applications. If noise is an issue, then the low pass filter can be moved to the output of the circuit to lessen its affect.

The only specification that clearly fails simulation is the output power at the 3dB compression point. This is the fault of the designer by mistakenly reading the wrong parameter throughout the design process. Other than that, the amplifier design shows effective use of the simulation tools and design techniques learned during the rf and microwave courses taught at JHU

## Appendix

This page should be printed and brought to the lab during testing.

#### S-Parameter Measurements

- 1. Power up the equipment.

- 2. Calibrate the network analyzer using open, short, thru, and load test fixtures.

- 3. Mount circuit on probe station and connect probes RF in, RF out, and both DC sources.

- 4. Set each DC supply to 1.5 volts and limit each current to 10mA.

- 5. Measure the s-parameters from 100 MHz to 8 GHz and note S21 at 2.305 GHz, 4 GHz and 5.875 GHz (see table below).

- 6. Save the s2p file.

#### **IP3** Measurements

- 1. Note the power losses in the cables.

- 2. Connect the signal generator to the input of the device.

- 3. Connect the spectrum analyzer to the output of the device.

- 4. Connect and set the DC bias as above.

- 5. Set the frequency to 2.305 GHz and sweep the input power from -30 dBm to -10 dBm noting the output power at 2 dB intervals (see table below).

- 6. Repeat step 5 at 4 GHz.

- 7. Repeat step 5 at 5.875 GHz.

|                 | Gain           |               |

|-----------------|----------------|---------------|

| Frequency (GHz) | Simulated (dB) | Measured (dB) |

| 2.305           | 22.12          |               |

| 4               | 24.09          |               |

| 5.875           | 22.25          |               |

Cable loss at input

Cable loss at output

|           | Power            |              |                  |  |  |

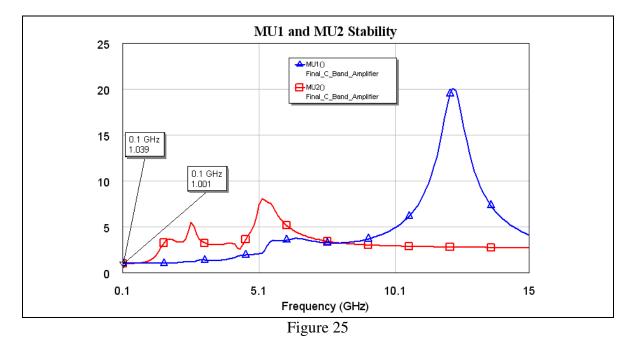

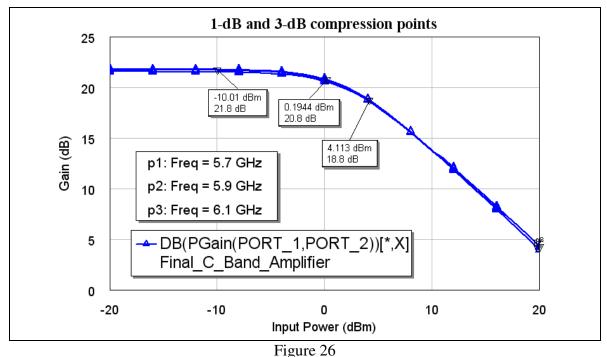

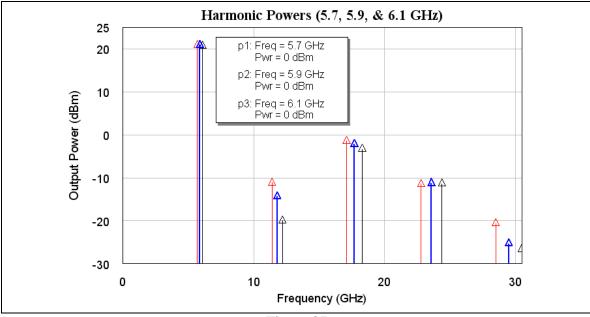

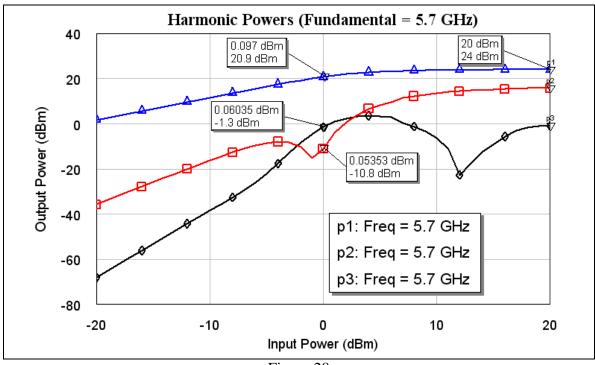

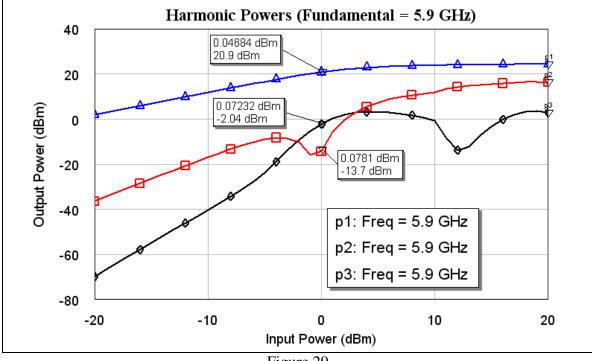

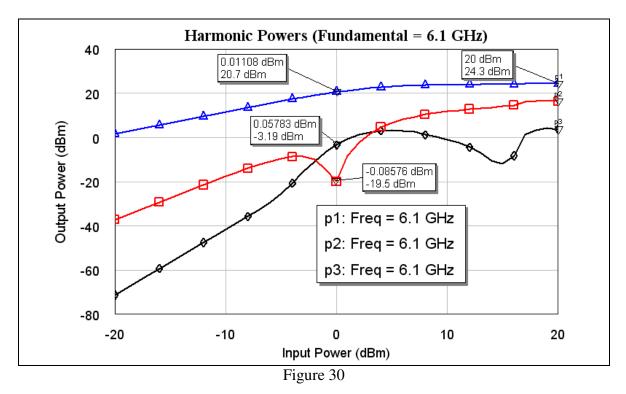

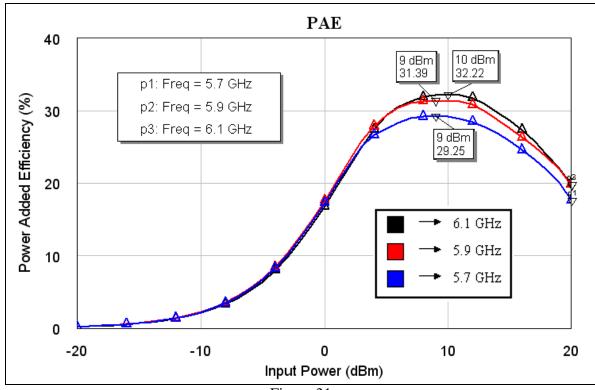

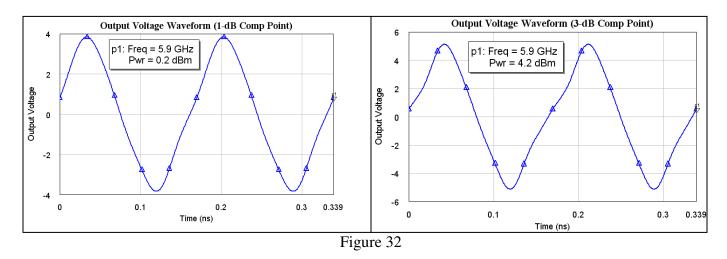

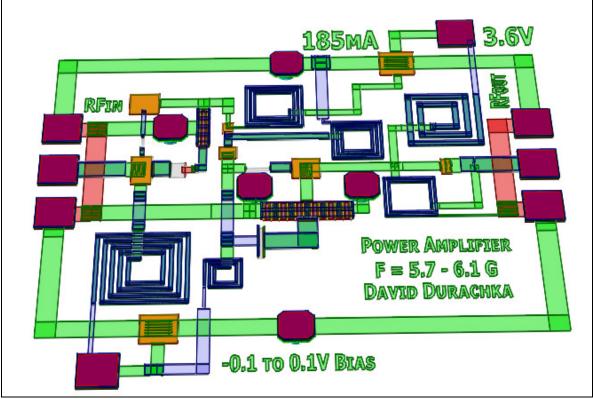

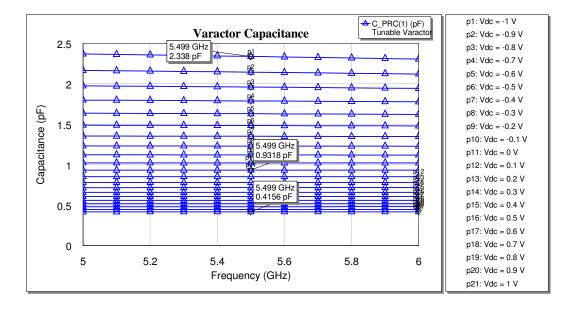

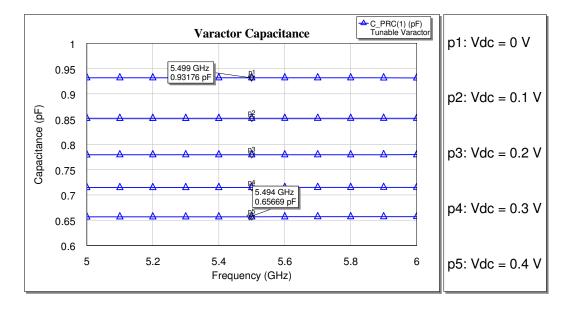

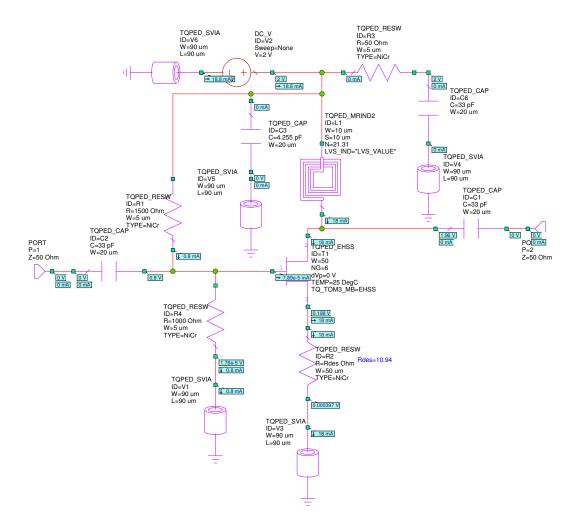

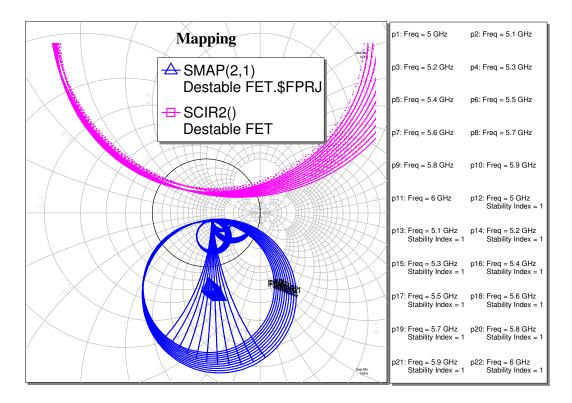

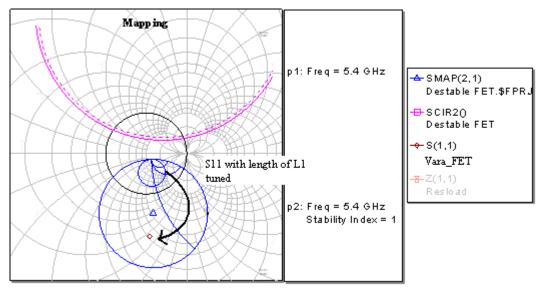

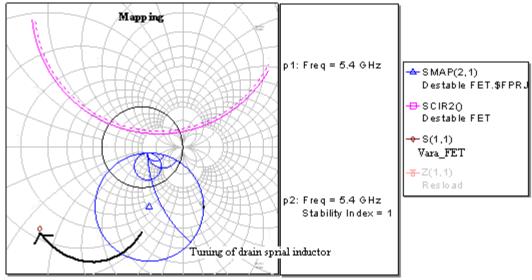

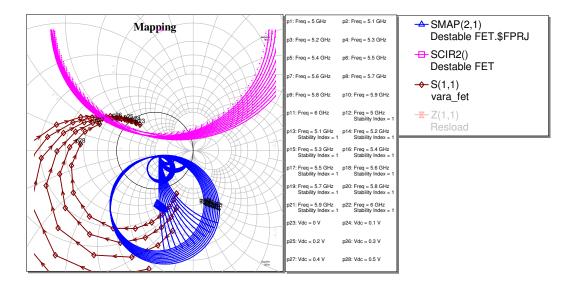

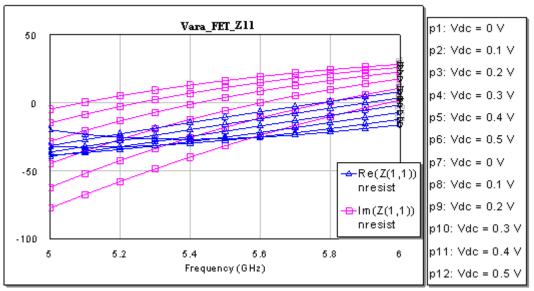

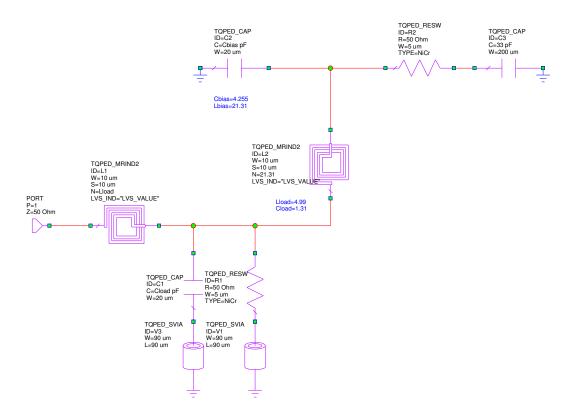

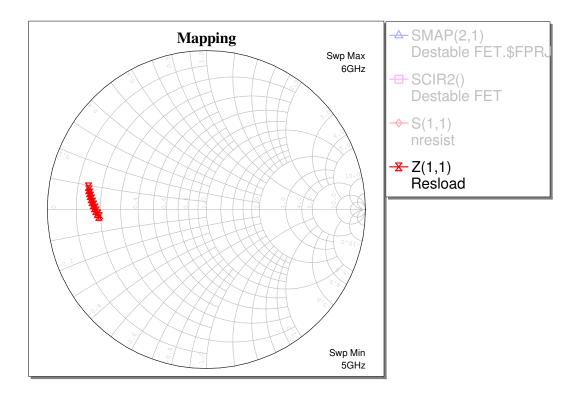

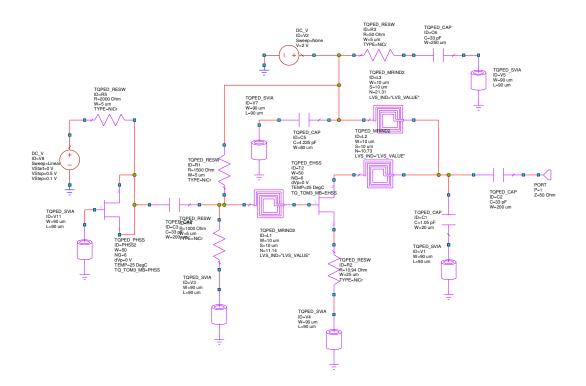

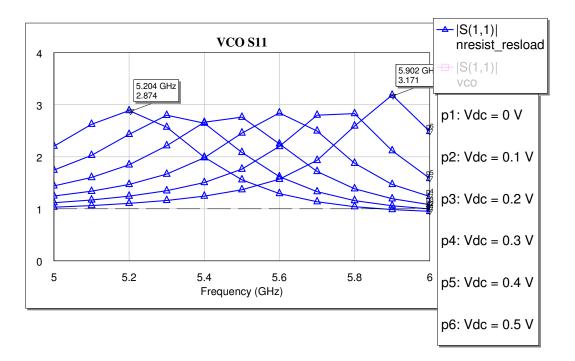

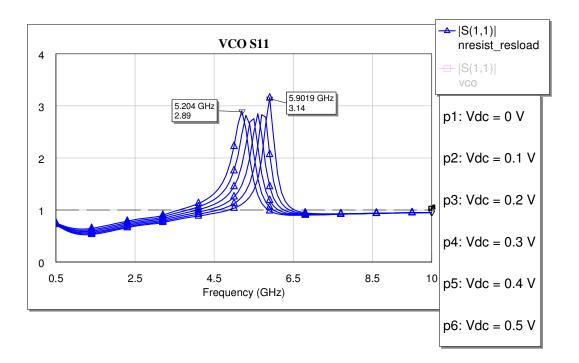

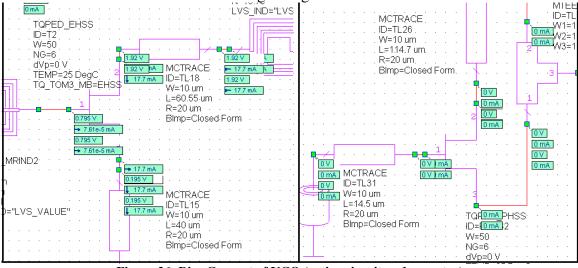

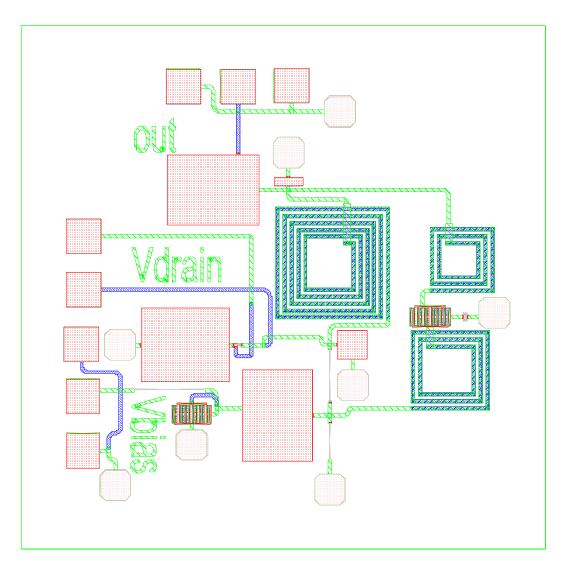

|-----------|------------------|--------------|------------------|--|--|